# **SmartCtrl User's Guide 2025.1**

by Power Smart Control S.L.

# SmartCtrl User's Guide ☐

**2024.1 version**

## **Contact and Support**

Power Smart Control S.L. is dedicated to assisting and supporting users. For inquiries or assistance, please reach out to Power Smart Control S.L. via email at:

support@powersmartcontrol.com

sales@powersmartcontrol.com

SmartCtrl Copyright © 2015-2025 Power Smart Control S.L.

All Rights Reserved.

No part of this User's Guide may be reproduced or modified in any form or by any means without the written permission of Power Smart Control S.L.

### **Notice**

Power Smart Control User's Guide, tutorials or other design advice, services or information, including, but not limited to, reference designs, are intended to assist designers who are developing applications that use SmartCtrl; by downloading, accessing or using any particular Power Smart Control resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this notice.

Power Smart Control reserves the right to make corrections, enhancements, improvements and other changes to its resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications with all applicable regulations, laws and other applicable requirements.

#### Disclaimer and limitation of liability

Power Smart Control S.L. makes no representation or warranty with respect to the adequacy or accuracy of this documentation or the software which it describes. Power Smart Control S.L. does not warrant that the software will be uninterrupted or that the operation of the software will be error-free. Power Smart Control S.L. disclaims all representations and warranties, express or implied, as to the software and documentation, including, without limitation, any warranty of merchantability, accuracy, completeness, fitness for any particular purpose, non-infringement, or likelihood of success. In no event will Power Smart Control S.L. or its direct or indirect suppliers be liable for any damages whatsoever including, but not limited to, direct, indirect, incidental, or consequential damages of any character including, without limitation, loss of business profits, data, business information, or any other commercial damages or losses, or for any damages in excess of the list price for the product. In no event shall Power Smart Control S.L. aggregate cumulative liability for any claims arisings out of or related to the software exceed the fees or price paid for the software during the preceding twelve-month period.

In addition, the following aspects shall apply:

- 1. Changes and updates: Power Smart Control S.L. is committed to continuous improvement in its products, and, therefore, reserves the right to modify them without prior notification.

- 2.Accuracy of Information: Despite our efforts to provide accurate information, Power Smart Control S.L. does not guarantee the accuracy or completeness of the information contained in the software and documentation. Users assume the responsibility to verify any critical information regarding the software and documentation for their specific applications.

- 3.Restrictions on Product Usage and Integration: Unauthorized distribution, replication, or reverse engineering of the software by users is strictly prohibited without explicit written permission from Power Smart Control S.L. Additionally, users are prohibited from incorporating Power Smart Control S.L. software as a constituent part of their own products without obtaining written consent from Power Smart Control S.L.

- 4.Proper Use: It is the user's responsibility to use the software in accordance with the instructions provided in this document and applicable laws. Power Smart Control S.L. shall not be liable for damages resulting from improper use, negligence, or unauthorized modifications to the software.

- 5.Liability for Damages/Losses: Power Smart Control S.L. shall not be liable for direct, indirect, incidental, consequential, or special damages/losses (of any nature, without limitation) that may arise from the use of the software, even if the possibility of such damages/losses has been advised.

- 6.Unauthorized Modifications: Any alterations made to the product, tampering with warranty seals, or suspicion of product modification by users will result in an immediate nullification of the warranty provided by Power Smart Control S.L.

- 7.Regulatory Compliance: It is the user's responsibility to ensure that the use of the software complies with all applicable regulations and standards in their jurisdiction.

By using this software, the user agrees to the terms and conditions outlined in this clause of disclaimer and limitation of liability, and acknowledges having read and understood the contents of this document.

# **Table of Contents**

| Part I | SmartCtrl                                                         | 8          |

|--------|-------------------------------------------------------------------|------------|

| 1      | Why SmartCtrl?                                                    | 8          |

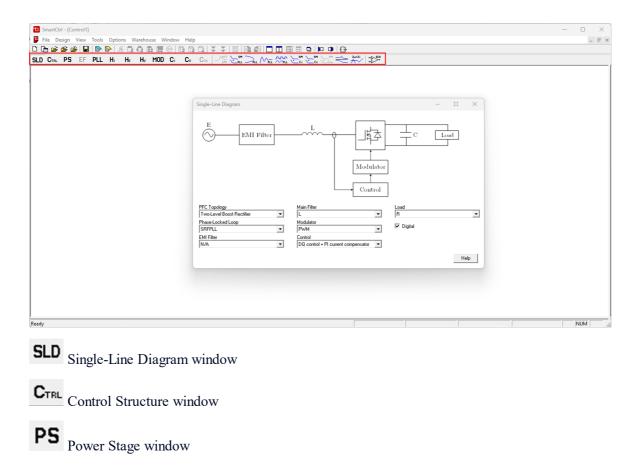

| 2      | Program Layout                                                    | 9          |

| 3      | Main menus and toolbars                                           | 12         |

|        | File Menu                                                         | 12         |

|        | Design Menu                                                       | 14         |

|        | Options Menu                                                      | 15         |

|        | View Menu                                                         | 16         |

|        | Tools Menu                                                        |            |

|        | Warehouse Menu                                                    |            |

|        | Window Menu                                                       |            |

|        | Help Menu                                                         |            |

|        | Main toolbar<br>View toolbar                                      |            |

| 4      |                                                                   |            |

| 4      | Design a predefined topology                                      |            |

|        | DC-DC power stage and control design                              |            |

|        | DC-DC Converter - Single loop                                     |            |

|        | DC-DC Converter - Peak Current Mode Control                       |            |

|        | DC-DC Converter - Average Current Control  Power factor corrector |            |

|        | Power stage                                                       |            |

|        | Graphic panels                                                    |            |

|        | Oscillator ramp and internal compensator                          |            |

|        | Line current                                                      | 69         |

|        | Rectified voltage and external compensator output                 | 69         |

|        | Multipliers                                                       | 70         |

|        | Multiplier                                                        | 70         |

|        | UC3854A multiplier                                                | 71         |

| 5      | Desing a generic topology                                         | 72         |

|        | s-domain model editor                                             | 73         |

|        | Import frequency response data from .txt file                     | 74         |

|        | s-domain model (equation editor)                                  |            |

|        | s-domain model (equation editor) VMC                              |            |

|        | s-domain model (equation editor) CMC                              |            |

|        | s-domain model (polynomial coefficients)                          |            |

| •      | Plant wizard                                                      |            |

| 6      |                                                                   |            |

|        | Plant (equation editor)                                           |            |

|        | Sensor (equation editor)                                          |            |

| _      | Compensator (equation editor)                                     |            |

| 7      |                                                                   |            |

|        | Buck                                                              |            |

|        | Boost                                                             |            |

|        | Buck-boost                                                        | 129<br>132 |

|        |                                                                   |            |

|   | Forward                                               | 135 |

|---|-------------------------------------------------------|-----|

|   | Phase Shifted Full Bridge                             | 138 |

|   | Phase Shifted Dual Active Bridge (VMC RL - V1 to V2)  | 141 |

|   | Phase Shifted Dual Active Bridge (VMC ERL - V1 to V2) | 151 |

|   | Phase Shifted Dual Active Bridge (CS ERL - V1 to V2)  | 162 |

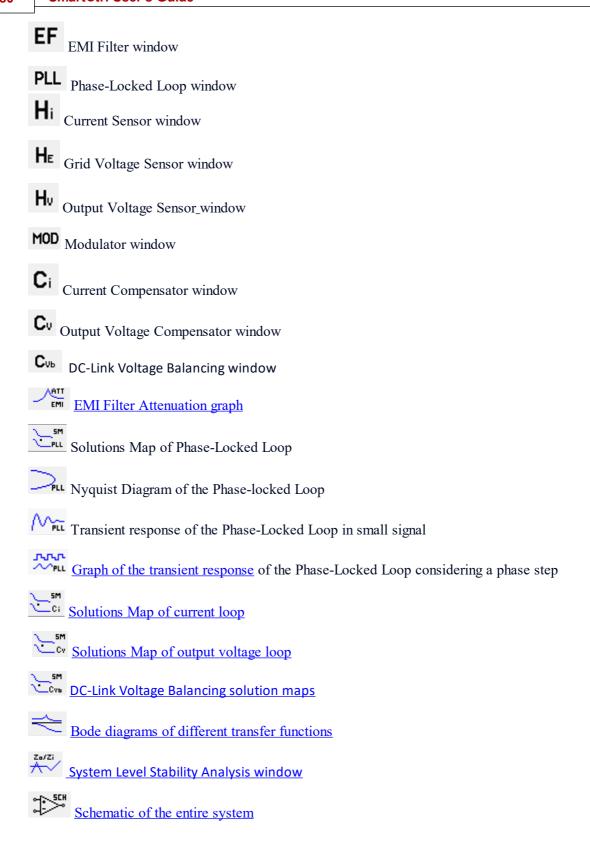

| 8 | Three-Phase PFC Converter                             | 173 |

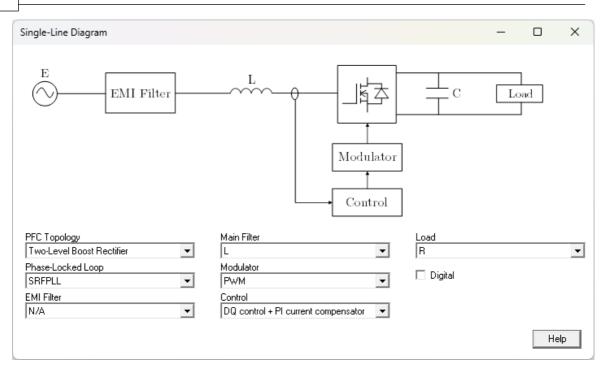

|   | Single-Line Diagram                                   | 173 |

|   | System Level Stability Analysis                       |     |

|   | Control Structure                                     |     |

|   | Power Stage                                           | 187 |

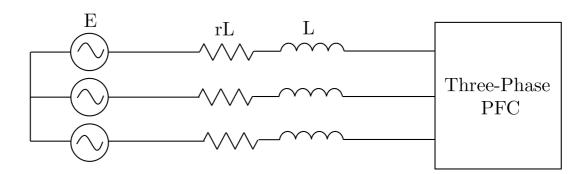

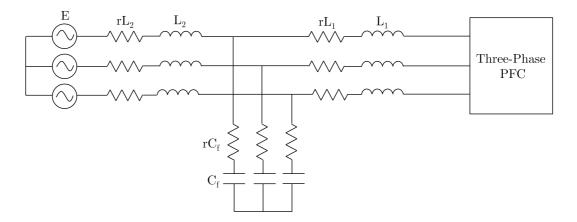

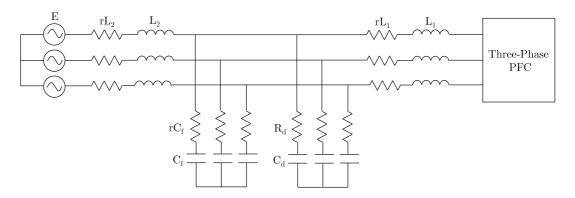

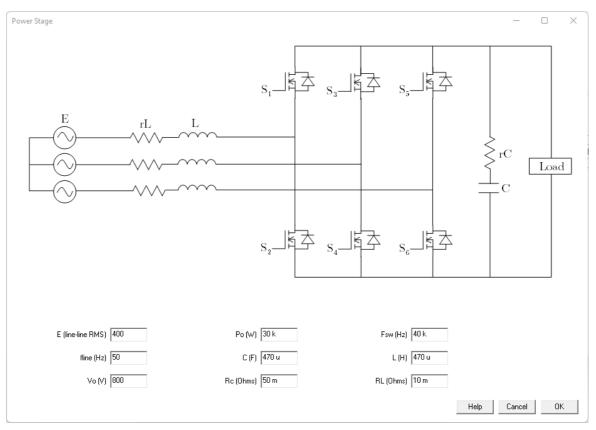

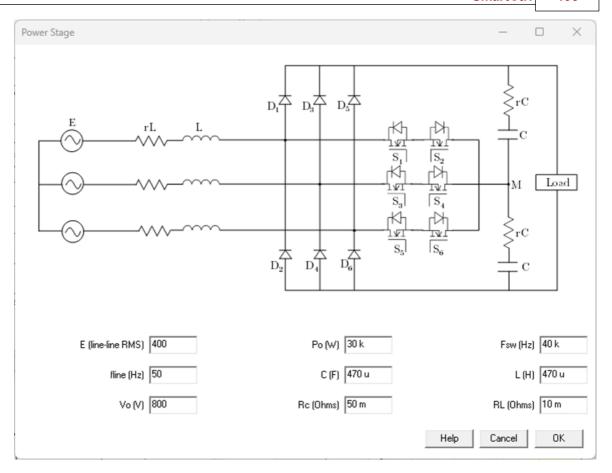

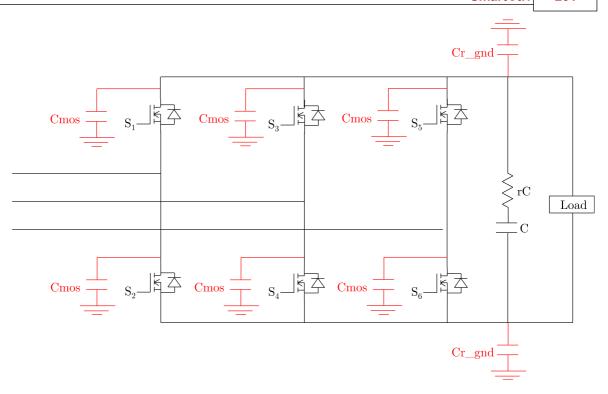

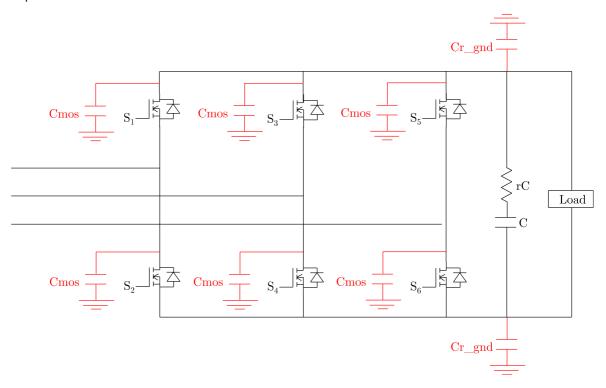

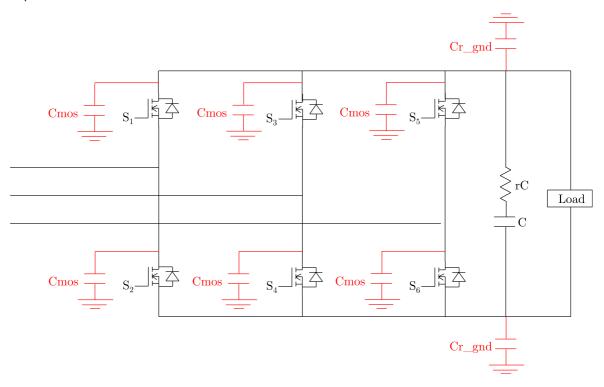

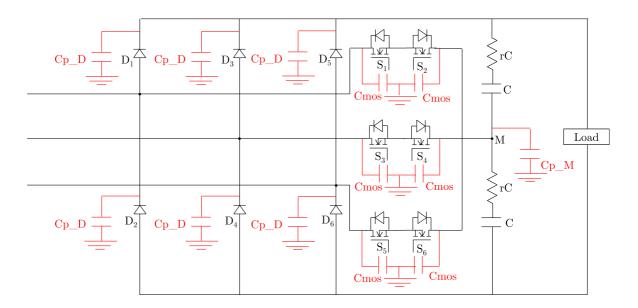

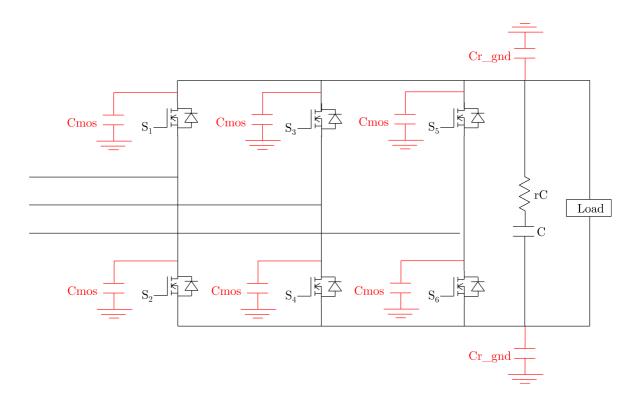

|   | Three-Phase Boost Rectifier                           | 187 |

|   | L                                                     | 188 |

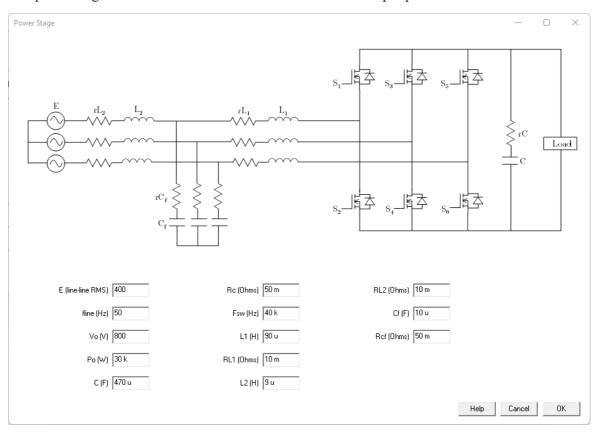

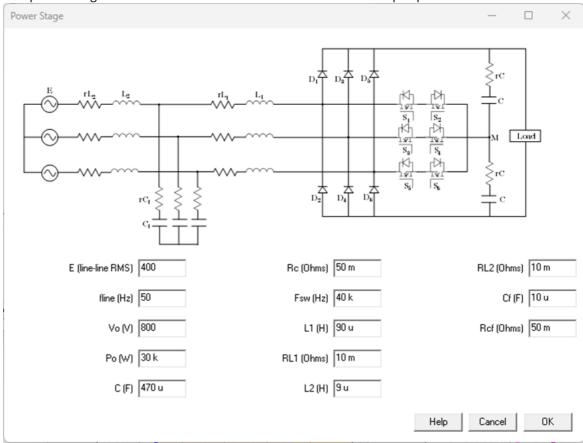

|   | LCL                                                   | 189 |

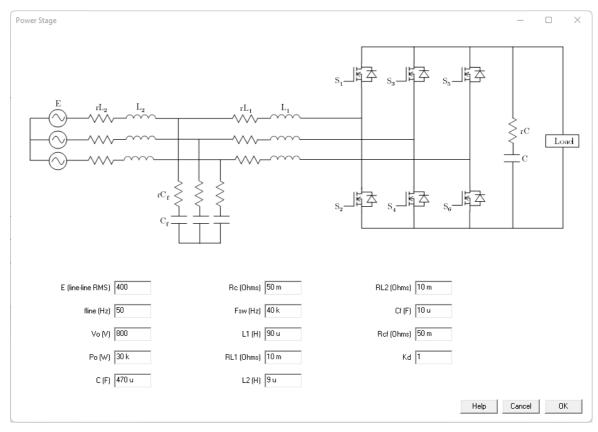

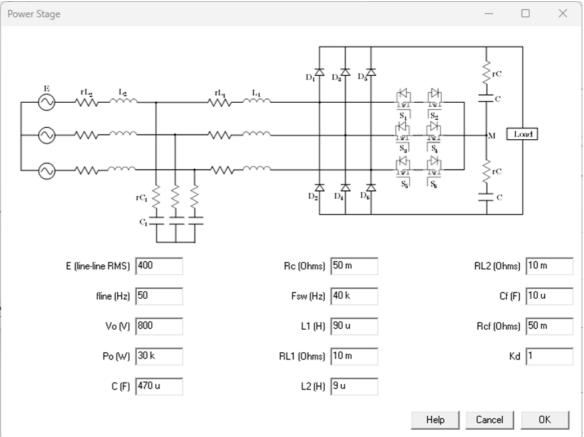

|   | LCL Active Damping                                    | 190 |

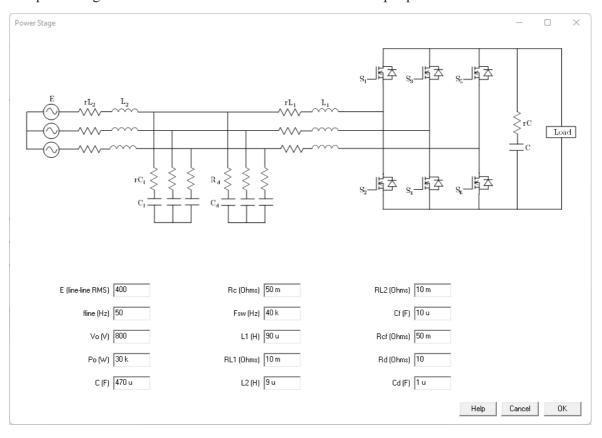

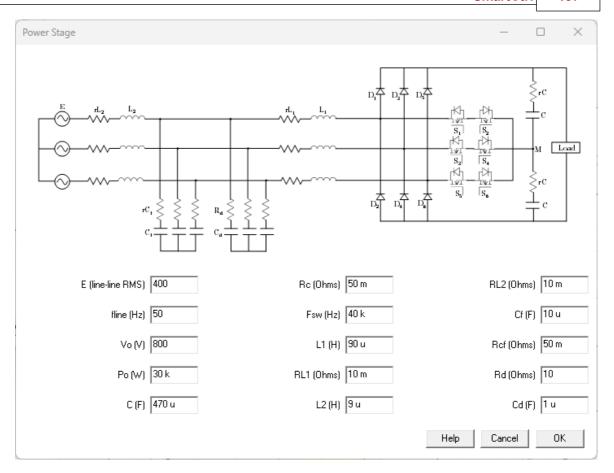

|   | LCL Passive Damping                                   | 191 |

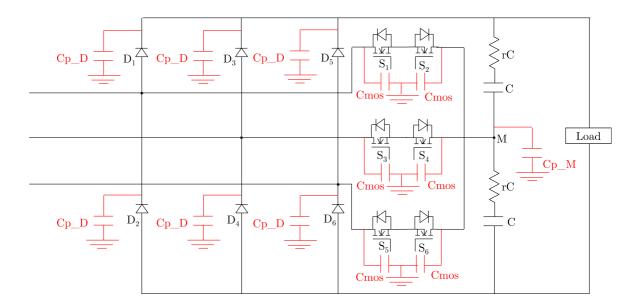

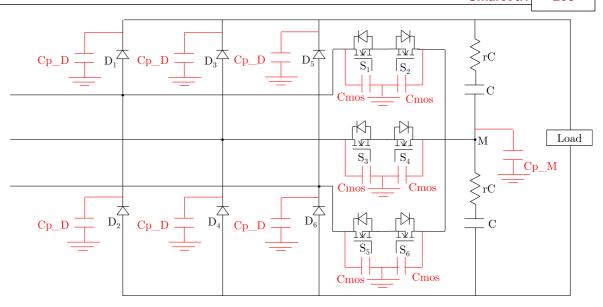

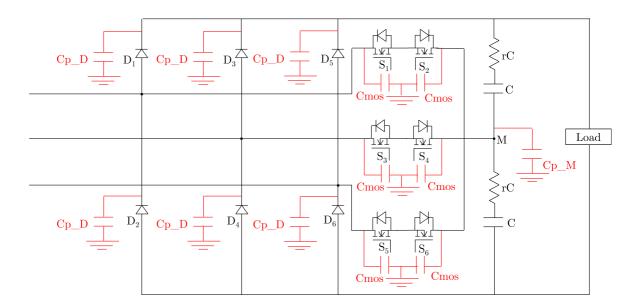

|   | Vienna Rectifier                                      | 192 |

|   | L                                                     | 192 |

|   | LCL                                                   |     |

|   | LCL Active Damping                                    |     |

|   | LCL Passive Damping                                   | 196 |

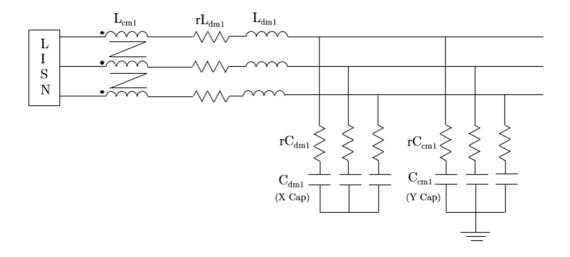

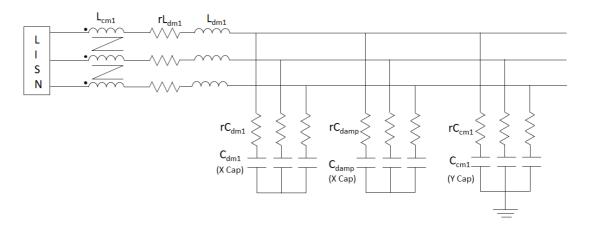

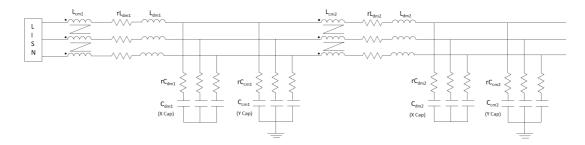

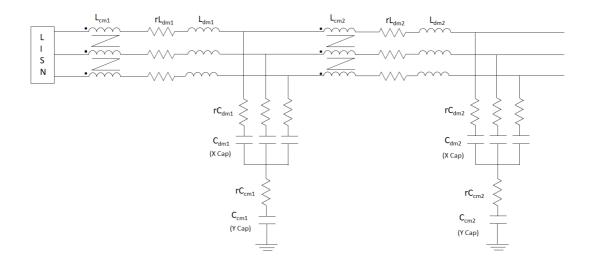

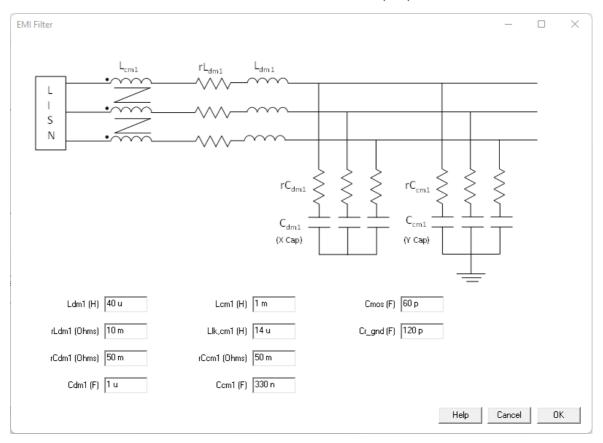

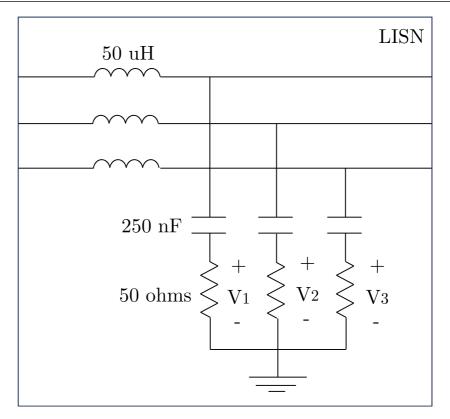

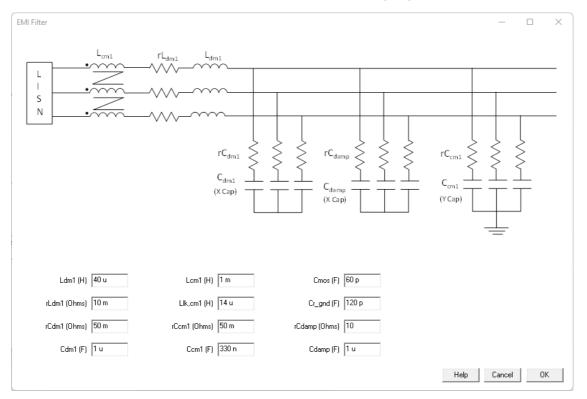

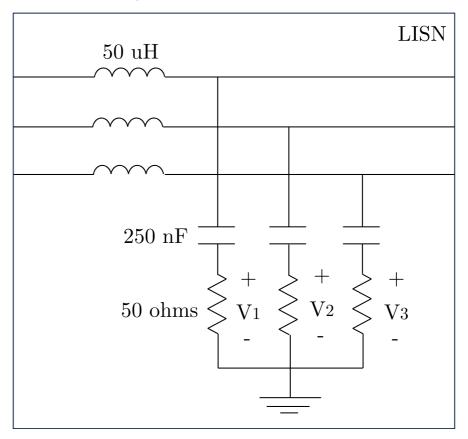

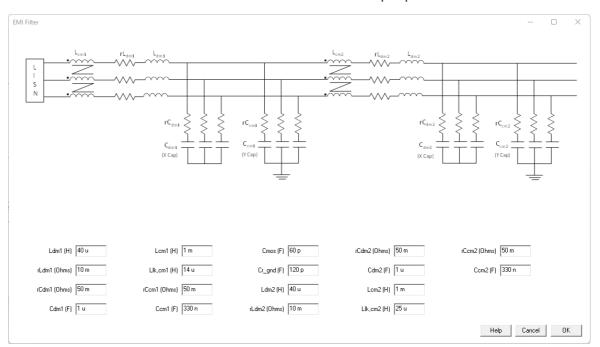

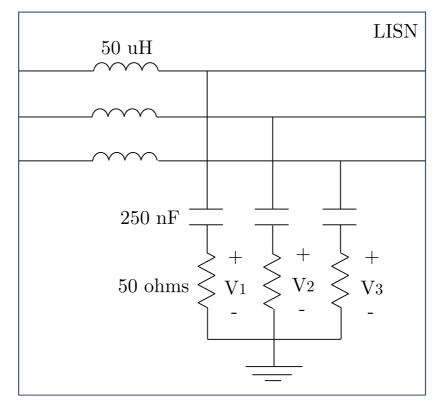

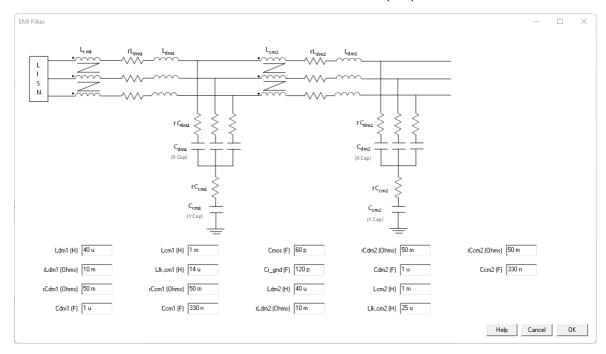

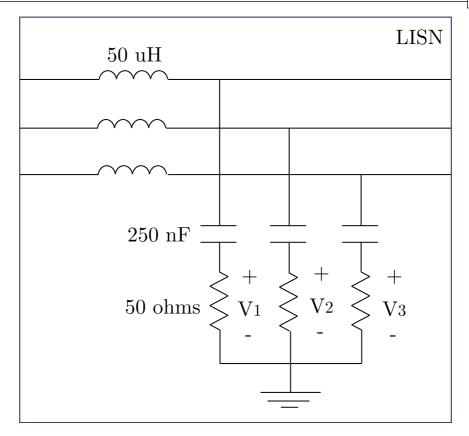

|   | EMI Filter                                            |     |

|   | Structure 1                                           |     |

|   | Structure 2                                           |     |

|   | Structure 3                                           |     |

|   | Structure 4                                           |     |

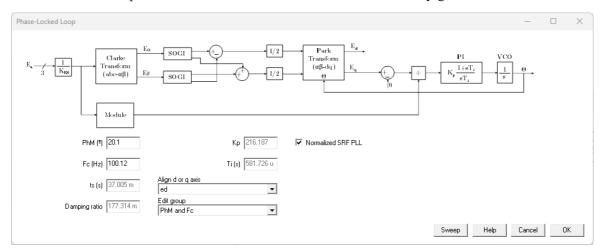

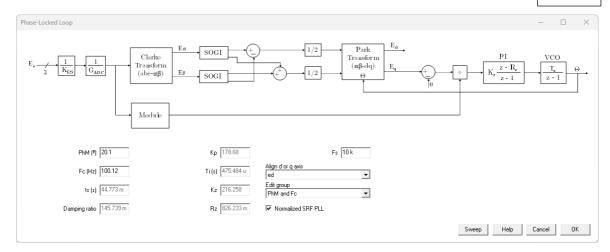

|   | Phase-Locked Loop                                     |     |

|   | SRFPLL                                                |     |

|   | QSG-SRFPLL                                            |     |

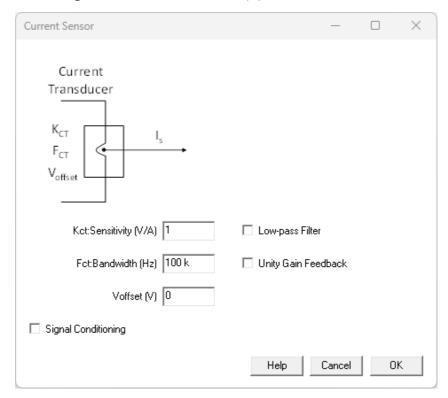

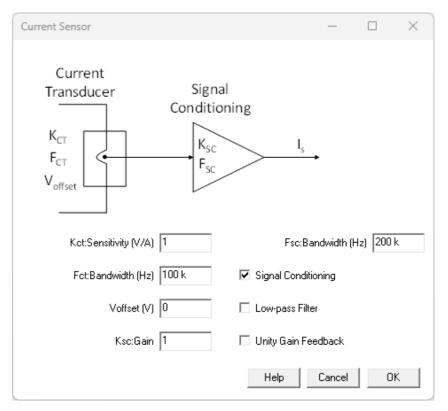

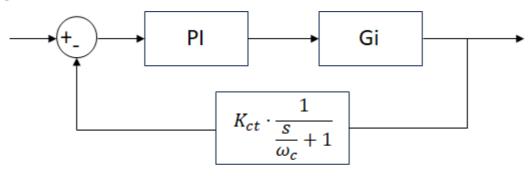

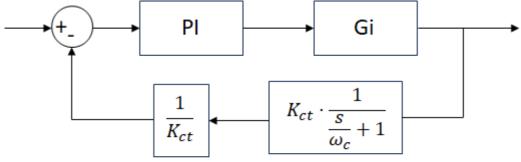

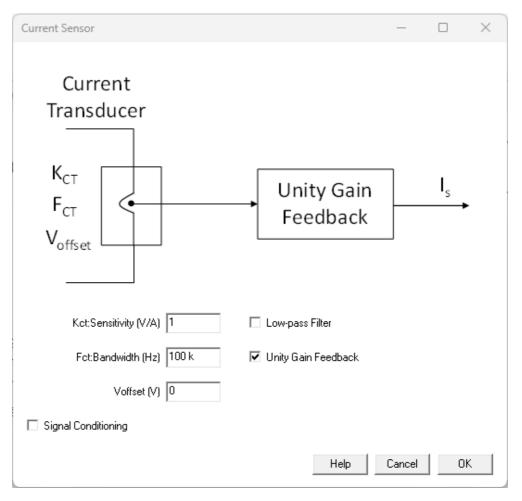

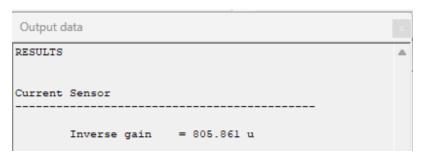

|   | Inductor current sensor                               |     |

|   | Grid Voltage sensor<br>Output voltage sensor          |     |

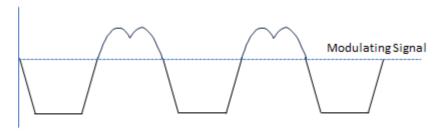

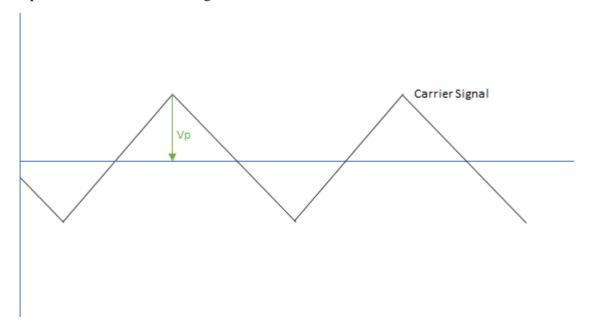

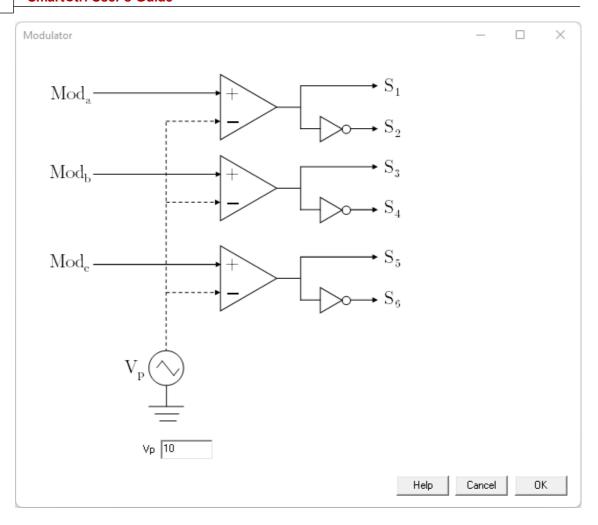

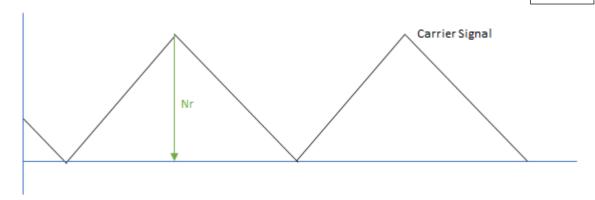

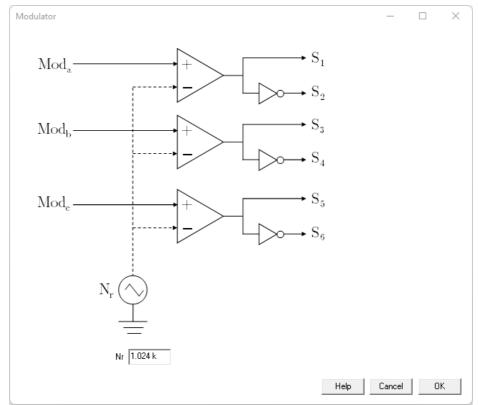

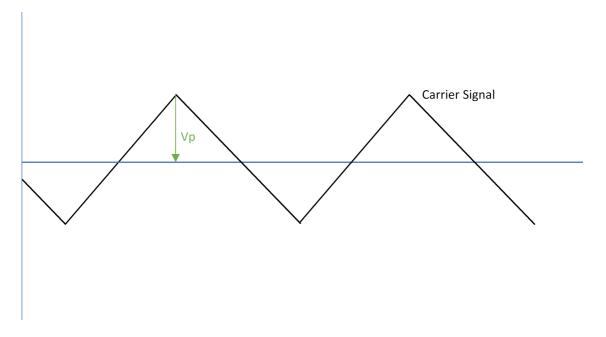

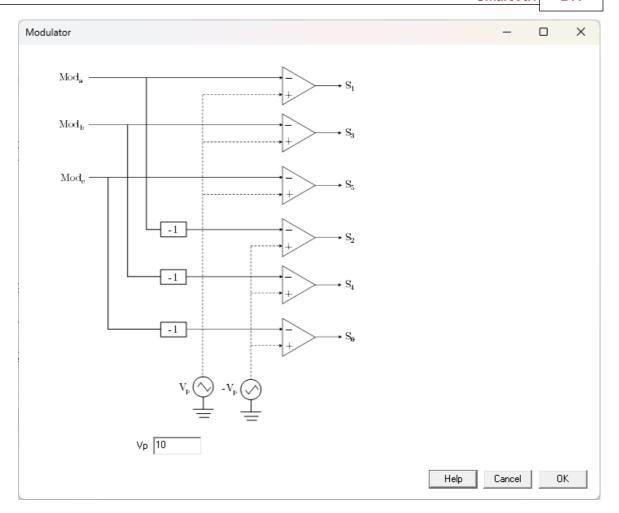

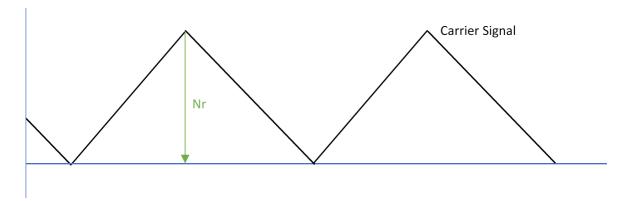

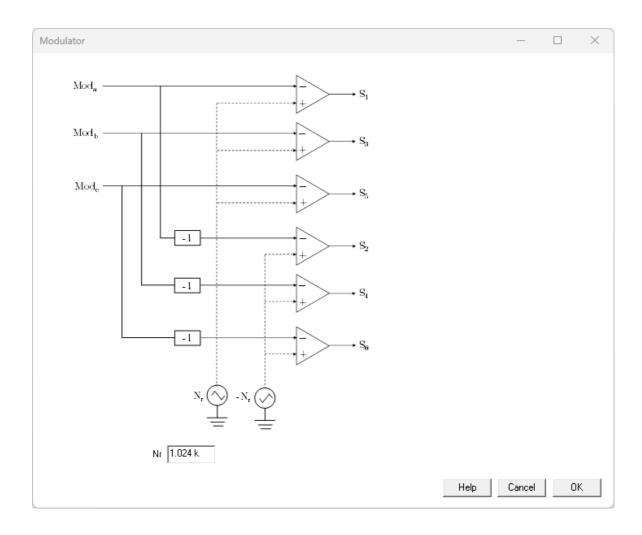

|   | Modulator                                             |     |

|   | Three-Phase Boost Rectifier                           |     |

|   | Analog                                                |     |

|   | Digital                                               |     |

|   | Vienna Rectifier                                      |     |

|   | Analog                                                |     |

|   | Digital                                               |     |

|   | Inductor Current Compensator                          |     |

|   | PI                                                    |     |

|   | P-Resonant                                            | 245 |

|   | Output Voltage Compensator                            | 248 |

|   | PI                                                    | 248 |

|   | DC-Link Voltage Balancing Compensator                 | 251 |

|   | PI                                                    | 252 |

|   | Export                                                | 253 |

|   | PSIM                                                  | 254 |

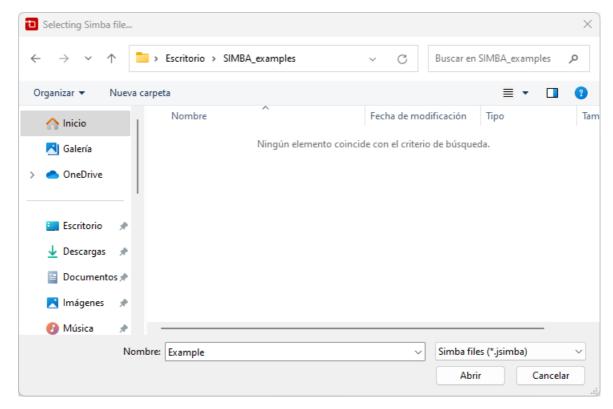

|   | SIMBA                                                 | 260 |

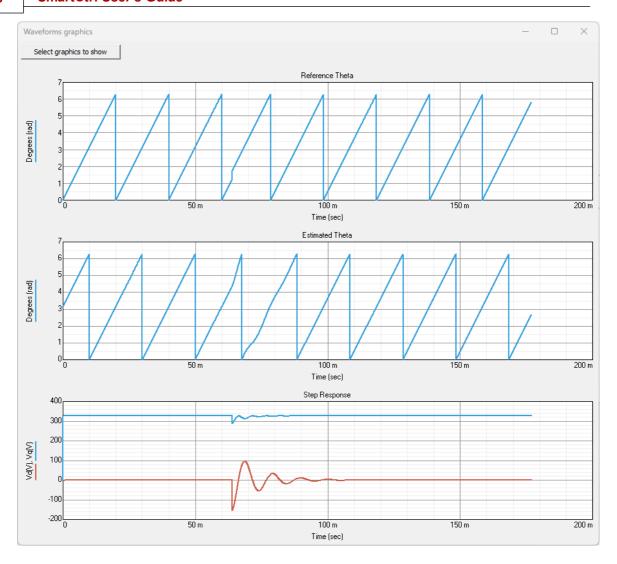

|   | Graphics                                              | 264 |

|   | Bode diagrams                                         | 264 |

|   | Waveforms of PLL                                      | 267 |

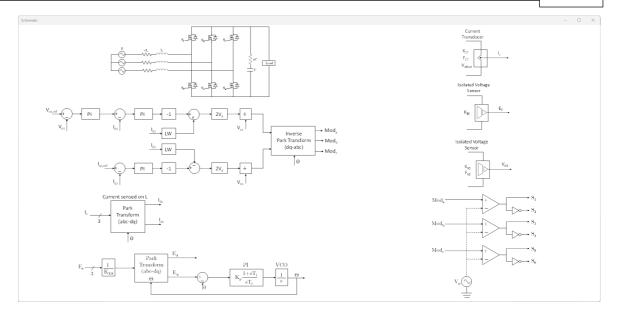

|   | Schematic                                             |     |

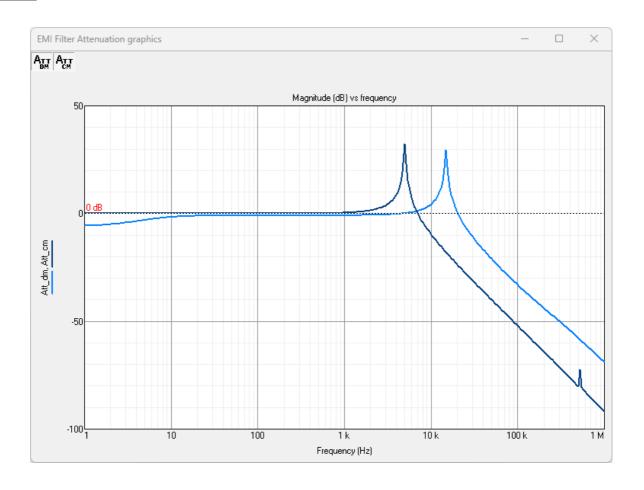

|   | EMI Filter Attenuation                                | 269 |

| 9 | Sensors                                               | 270 |

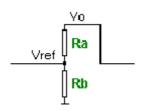

|    | Voltage divider                              | 270  |

|----|----------------------------------------------|------|

|    | Embedded voltage divider                     | 271  |

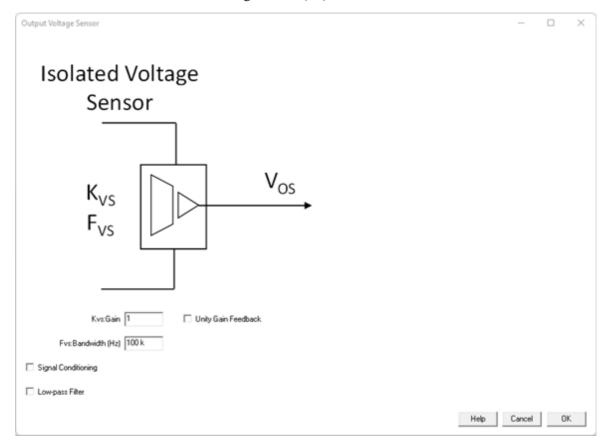

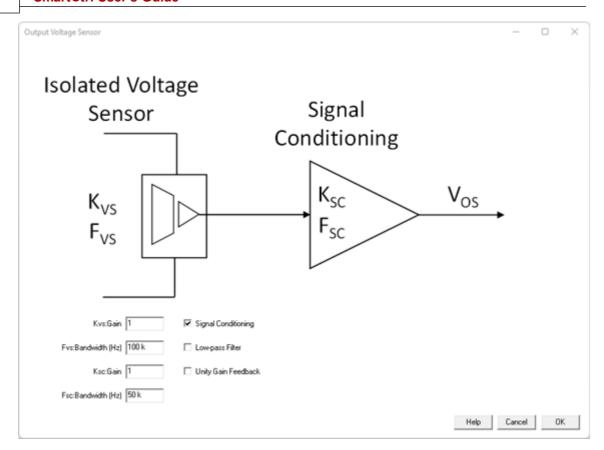

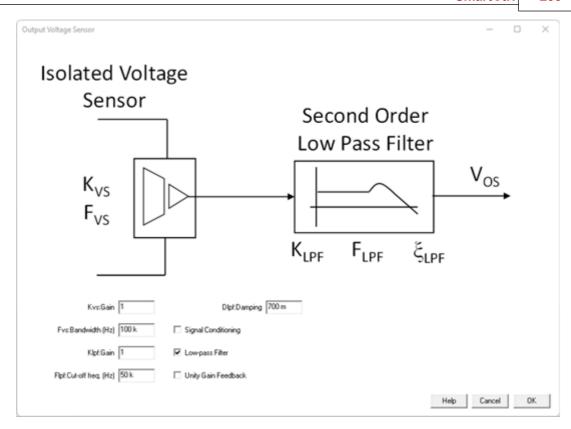

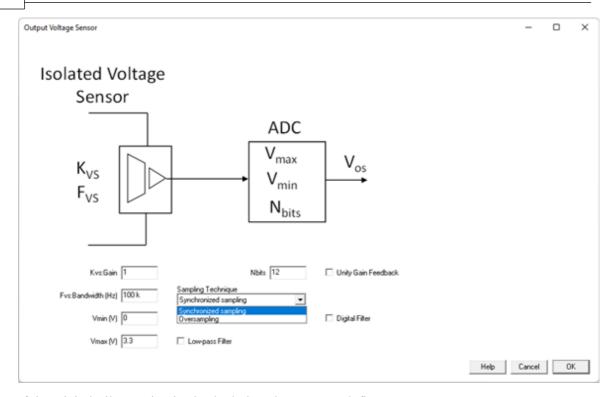

|    | Isolated Voltage Sensor                      | 272  |

|    | Resistive Sensor (Power Factor Corrector)    | 273  |

|    | Resistive Sensor (Peak Current Mode Control) | 274  |

|    | Hall effect sensor                           | 274  |

|    | Current sensor                               |      |

|    | User defined sensor                          | 275  |

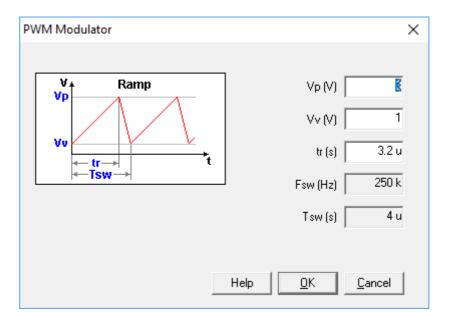

| 10 | Modulator                                    | 276  |

|    | Modulator (Peak Current Mode Control)        | 276  |

|    | Modulator (PWM)                              | 277  |

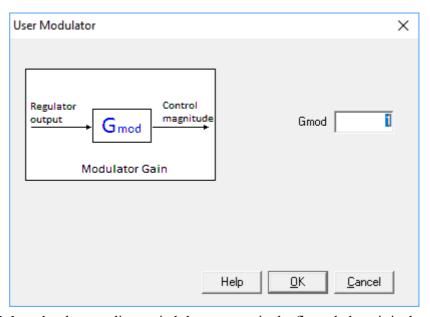

|    | User modulator                               | 279  |

| 11 | Compensators                                 | 280  |

|    | Analog compensators                          | 280  |

|    | Single loop or inner loop                    | 280  |

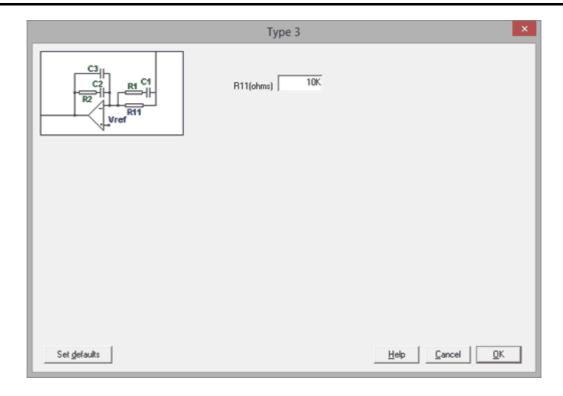

|    | Type 3 compensator                           | 280  |

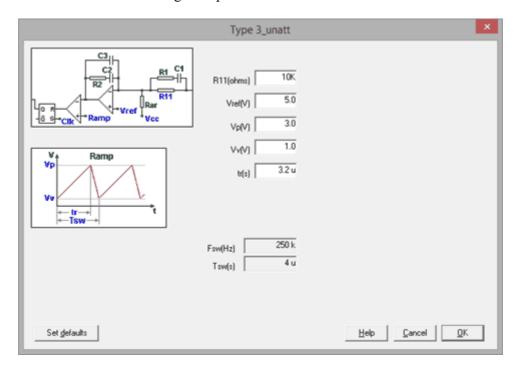

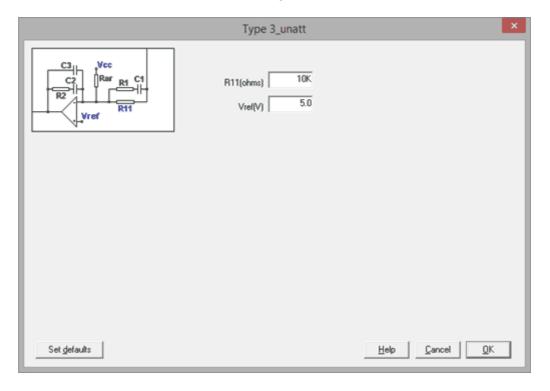

|    | Type 3 compensator unattenuated              | 281  |

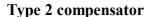

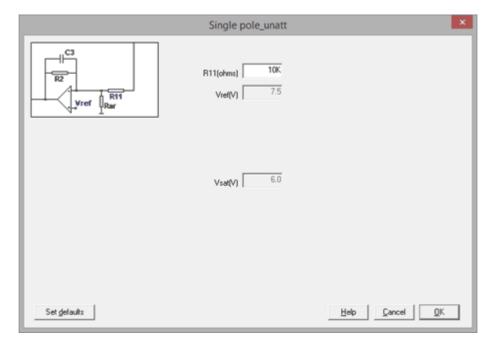

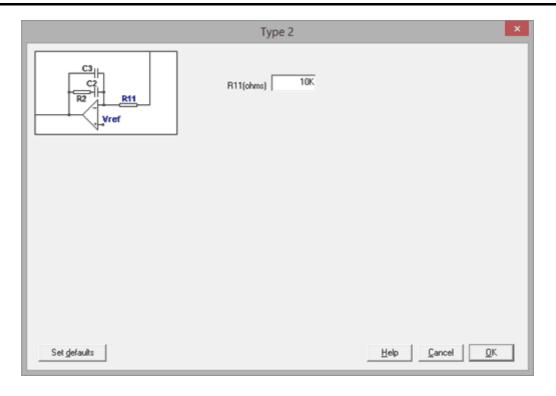

|    | Type 2 compensator                           | 283  |

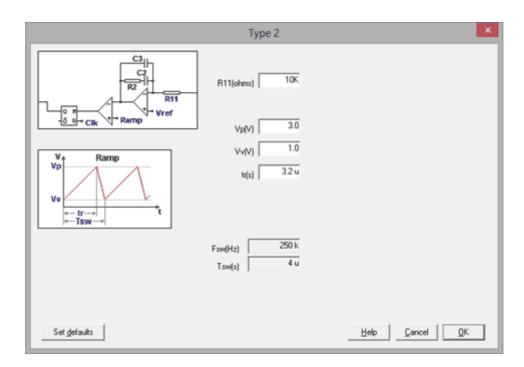

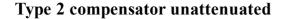

|    | Type 2 compensator unattenuated              | 284  |

|    | Planalog compensator                         | 285  |

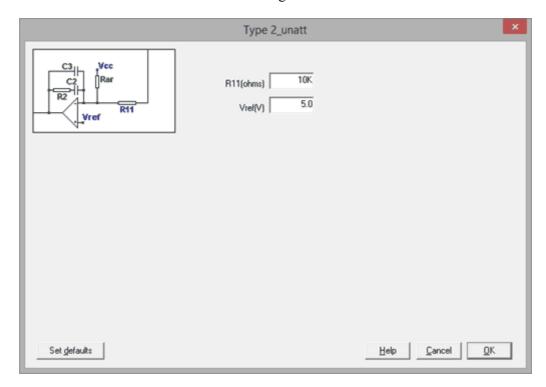

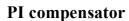

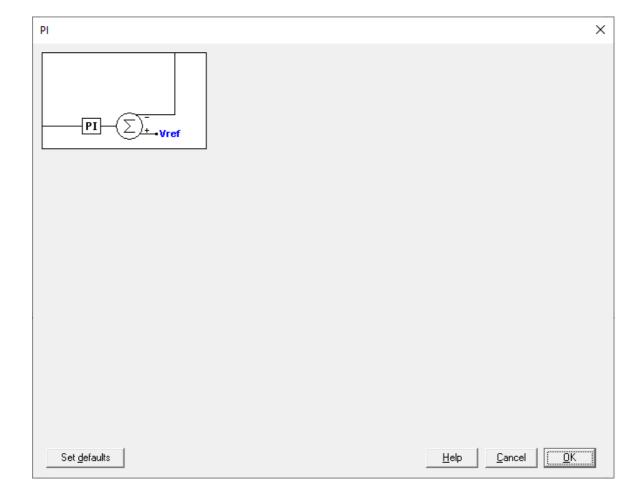

|    | PI compensator                               | 287  |

|    | PI compensator unattenuated                  |      |

|    | Outer Loop and Peak Current Mode Control     |      |

|    | Single Pole compensator                      |      |

|    | Single Pole unattenuated                     |      |

|    | Type 3 compensator                           |      |

|    | Type 3 compensator unattenuated              |      |

|    | Type 2 compensator                           |      |

|    | Type 2 compensator unattenuated              |      |

|    | PI analog compensator                        |      |

|    | PI compensator                               |      |

|    | PI compensator unattenuated                  |      |

|    | Digital compensators                         |      |

|    | PI Digital                                   |      |

|    | PID Digital  User defined compensator        |      |

| 40 | ·                                            |      |

| 12 | Graphic and text panels                      |      |

|    | Bode plots                                   |      |

|    | Nyquist diagram                              |      |

|    | Transient response plot                      |      |

|    | Steady-state waveforms                       |      |

| 40 | Text panels                                  |      |

|    | Solutions map                                |      |

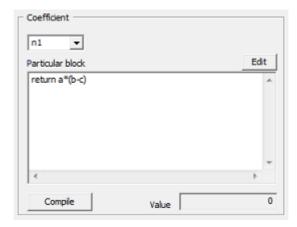

| 14 | Equation Editor                              | 323  |

|    | Editor box                                   | 331  |

| 15 | Import and Export                            | 332  |

|    | Export                                       | 332  |

|    | Export transfer function                     | 332  |

|    | Export to PSIM                               | 334  |

|    | Export transient responses                   | 340  |

|    | Export global                                |      |

|    | Export wayoforms                             | 2/1/ |

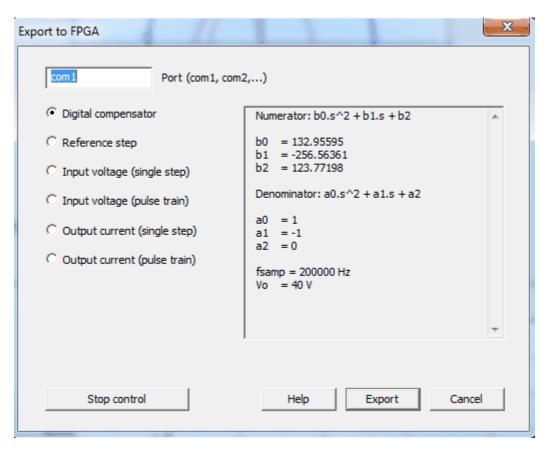

|    | Export to FPGA                          | 346                                    |

|----|-----------------------------------------|----------------------------------------|

|    | Import (Merge)                          | 349                                    |

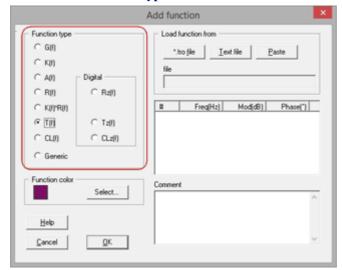

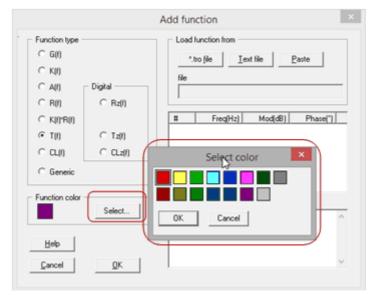

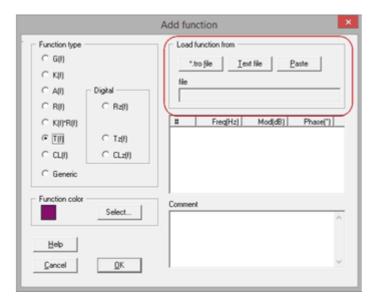

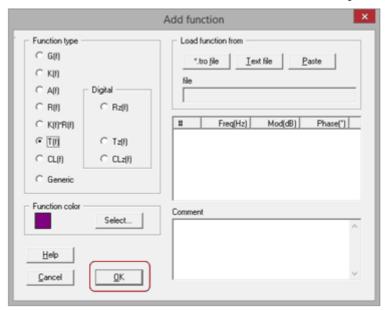

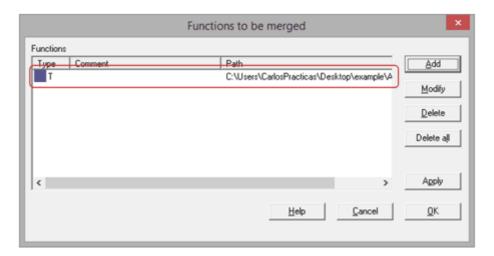

|    | Add Function                            | 351                                    |

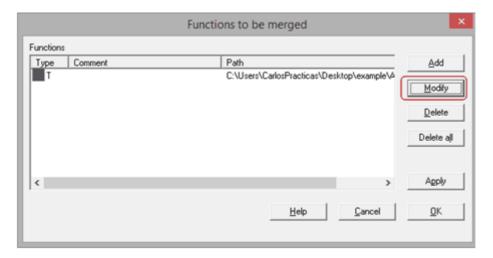

|    | Modify Function                         | 352                                    |

| 16 | Design Methods                          | 354                                    |

|    | K-factor method                         | 355                                    |

|    | Kplus method                            | 357                                    |

|    | Manual                                  | 358                                    |

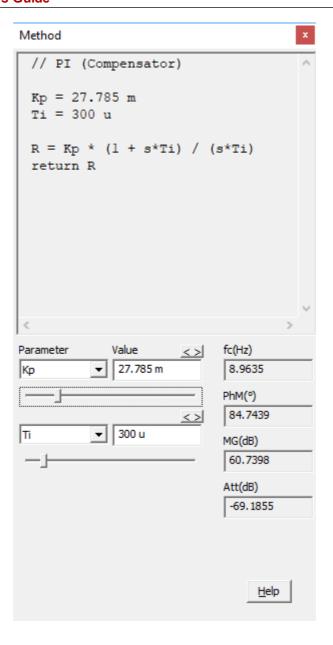

|    | PI tuning                               | 359                                    |

|    | Single Pole tuning                      | 363                                    |

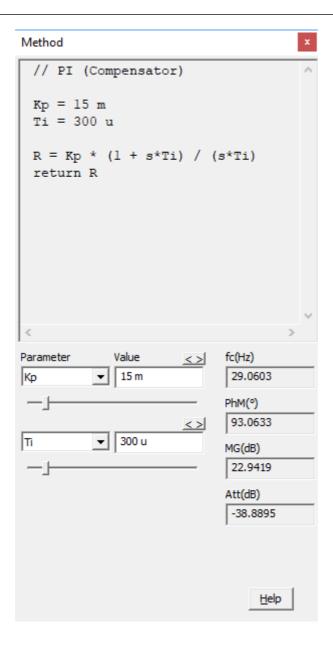

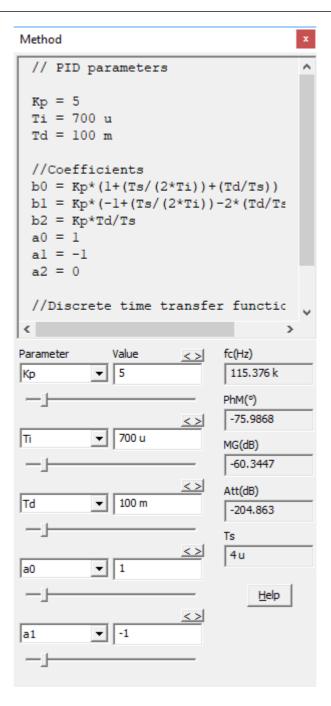

|    | Method box                              | 363                                    |

| 17 | Parametric Sweep                        | 364                                    |

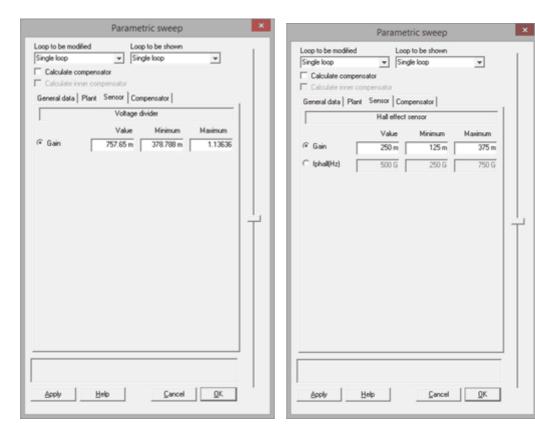

|    | Input parameters parametric Sweep       | 365                                    |

|    | Compensator Components Parametric Sweep | 369                                    |

|    | Source code parametric sweep            | 370                                    |

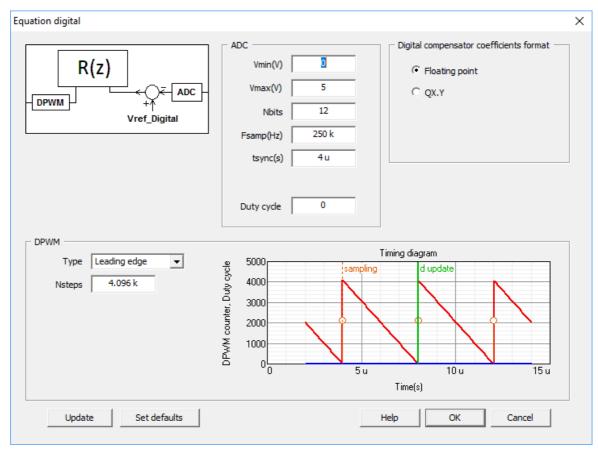

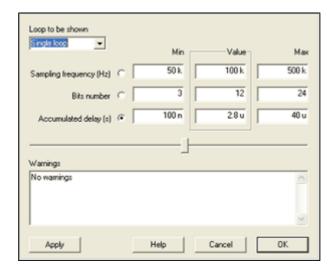

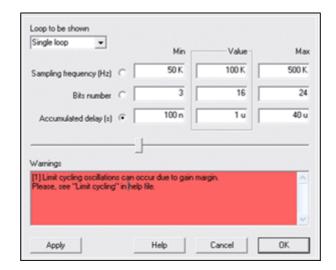

| 18 | Digital Control                         | 373                                    |

|    | Digital settings                        | 384                                    |

|    | Parametric sweep in digital control     | 387                                    |

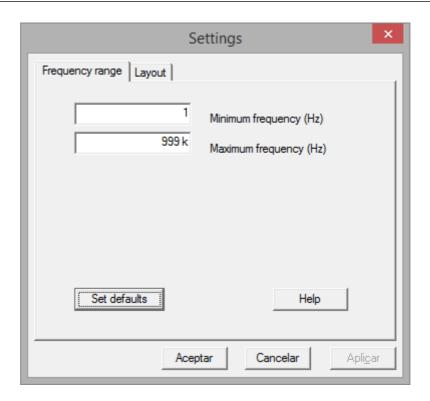

| 19 | Frequency settings                      | 389                                    |

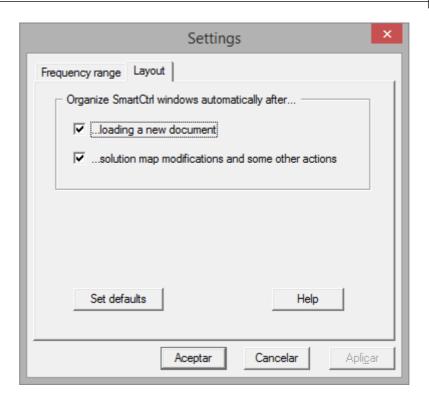

| 20 | Layout settings                         | 390                                    |

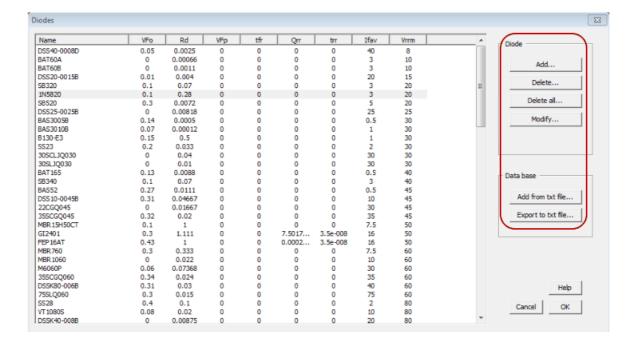

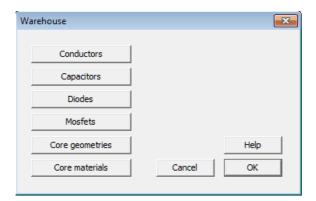

| 21 | Warehouse                               | 391                                    |

|    | Warehouse components                    | 392                                    |

|    | ······································  | ······································ |

## 1 SmartCtrl

## 1.1 Why SmartCtrl?

- 7 -

Navigation: SmartCtrl >

## Why SmartCtrl?

Top Next

SmartCtrl is the control designing tool for power electronics. It provides an easy to use interface for designing the control loop of almost any plant.

It includes the predefined transfer functions of some of the most commonly used power electronics plants, such as different DC-DC topologies, AC-DC converters, Inverters and motor drives.

However, it also allows the users to import their own plant transfer function by means of a text file. Therefore, this feature provides flexibility to design an optimize a control loop for almost any system, the plant, sensor and compensator can be user defined.

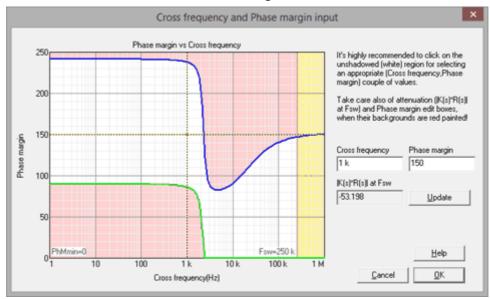

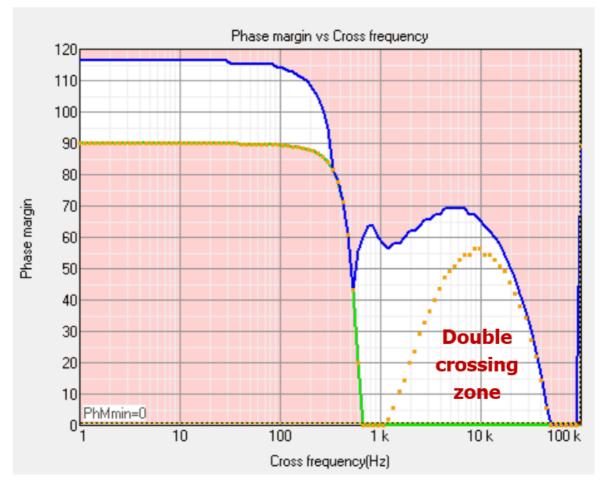

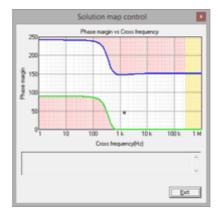

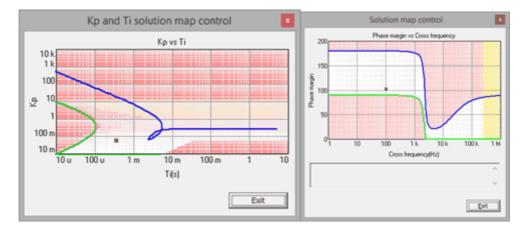

In order to ease the first attempt when designing a control loop, an estimation of the stable solutions space is given by the program under the name of "solutions map". Based on the selected plant, sensor and type of regulator, the solutions map provides a map of the different combinations of fc (Crossover Frequency) and phase margin that lead to stable systems.

Thus, the designer is able to select one of the points of the stable solutions space and to change the compensator parameters dynamically in order to adjust the system response to the user requirements in terms of stability, transient response, etc. since the program provides, at a glance, the frequency response of the system as well as the transient response and the compensator component values for the open loop given features. All of them are real time updated when any parameter of the system is varied by the designer.

The user can also work in S-domain or in Z-domain, for real digital control applications.

## **Key Features**

✓ Pre-defined transfer functions of commonly used DC-DC converters, Power Factor Correction converters, sensors and regulators.

- ✓ Different control techniques for DC-DC converters are supported:

- oSingle control loop structures: voltage mode control and current mode control.

- oPeak current mode control.

- OAverage current mode control implemented by means of two nested control loops

- ✓ Capability of designing the controller of any converter by means of:

- o Modeling the converter using the basic models provided.

- o Importing its frequency response data from a .txt file.

- o Defining its transfer function through the equation editor.

- ✓ Capability of designing a generic control system, with customer definition for the plant, sensor and compensator.

- ✓ Real Digital control: working directly in Z-domain.

- ✓ Estimation of the stable solutions space ("Solutions Map").

- ✓ Sensitivity analysis of the system parameters.

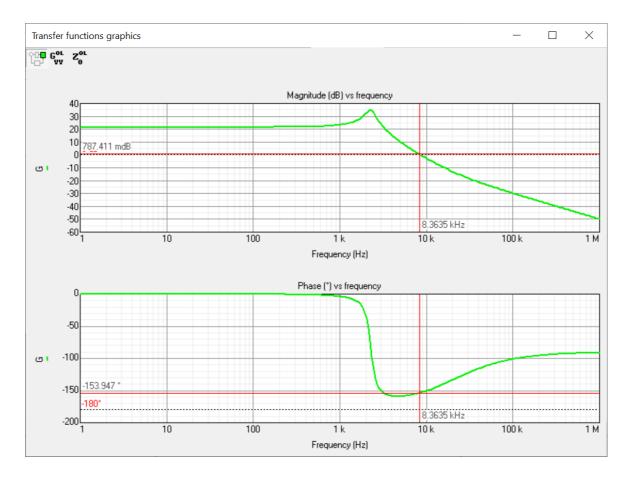

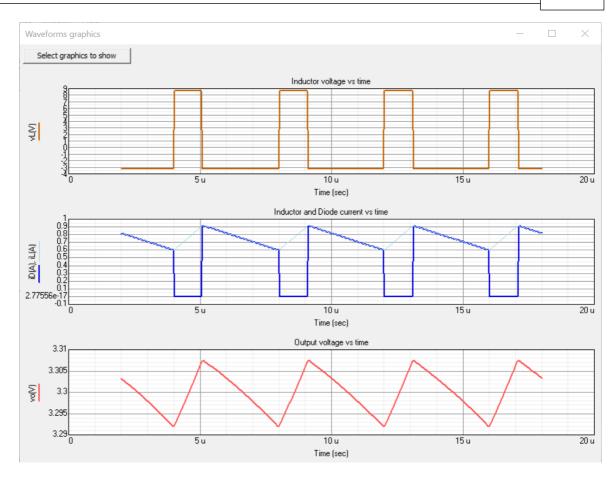

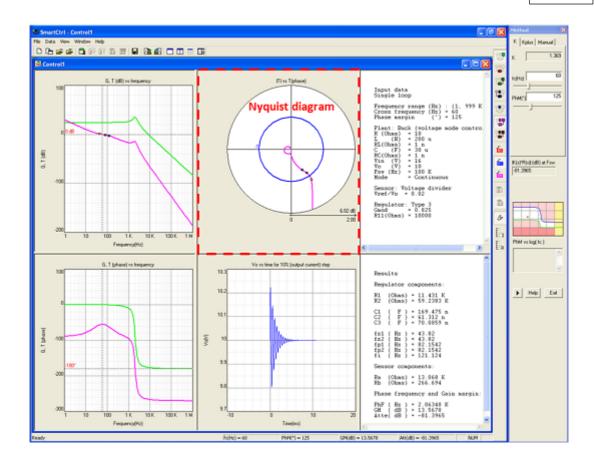

- ✓ Real time updated results of the frequency response (Bode and Nyquist plots), transient response and the steady state waveforms.

- ✓ Possibility of importing and exporting any transfer function by means of .txt files.

## 1.2 Program Layout

Navigation: SmartCtrl >

## **Program Layout**

Previous Top Next

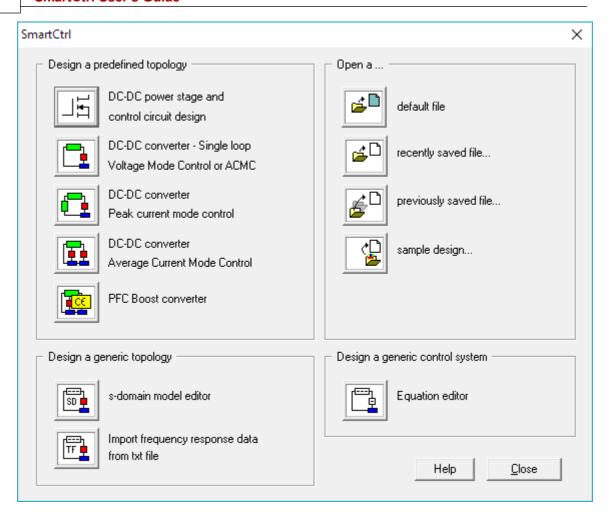

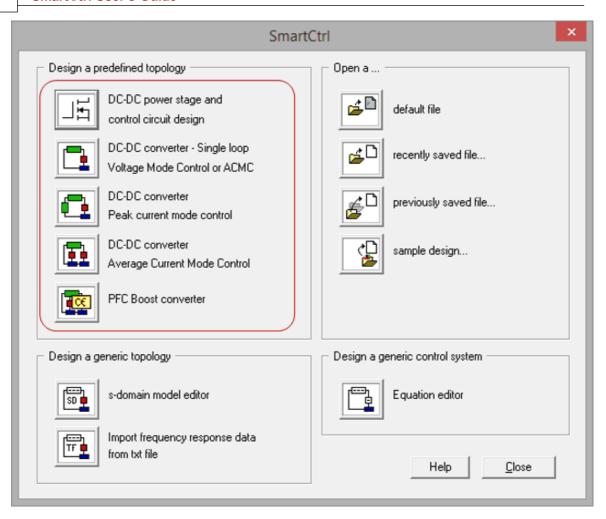

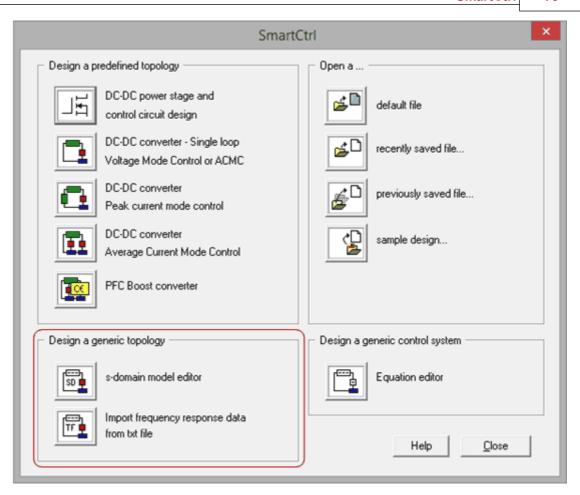

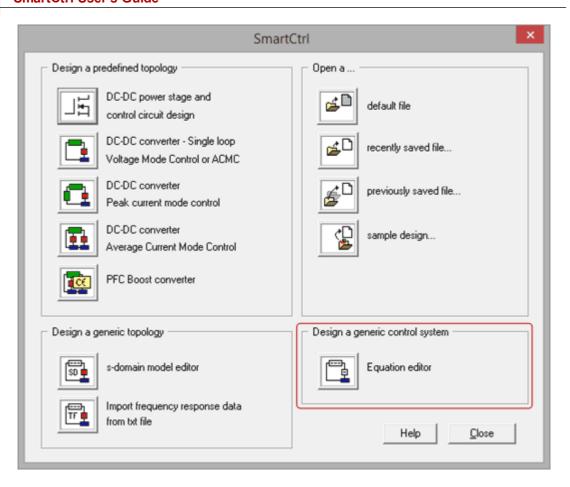

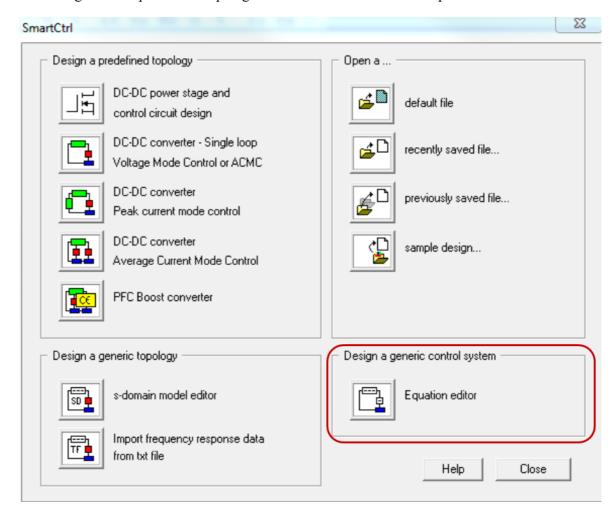

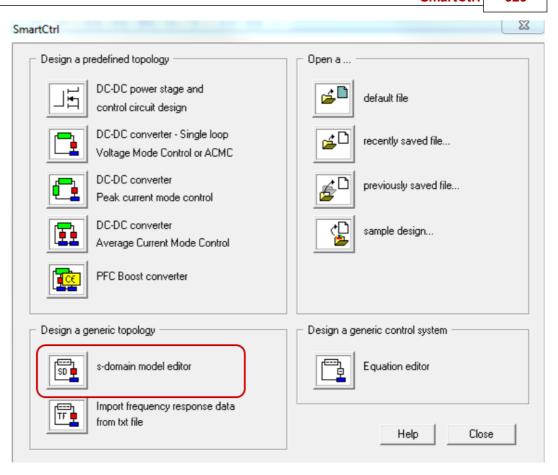

When SmartCtrl is started, all the available options are shown, and the user can select which of them is going to use. The aforementioned window is shown below. It is divided into four sections:

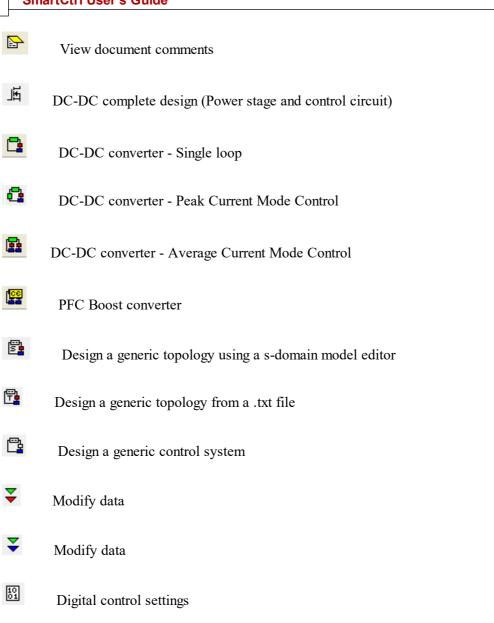

#### 1. Design a predefined topology

This option provides an easy and straightforward way of designing the control circuit of the most widely used power converters. Through a guided process, the user will be able to select amongst different control strategies:

- •DC-DC Power Stage and Control Circuit Design

- •DC-DC Converter- Single loop

Two different control strategies are available in this case: voltage mode control and current mode control.

- •DC-DC Converter Peak Current mode control

- •DC-DC Converter Average current mode control

Two nested loops are needed to implement the average current mode control. The outer loop is a voltage mode control loop, and the inner one is a current mode control.

• PFC Boost converter

## 2. Design a generic topology.

This option allows to design a converter by two different ways:

- •s-domain model editor.

- •Importing the frequency response data from .txt file

## 3. Design a generic control system - Equation editor.

SmartCtrl also provides the option of defining the whole system though its equation editor. And so, help the user though the designing process of any control problem regardless its nature, for example temperature control, motor drives, etc

#### 4. **Open...**

**Default file.** It opens a pre-designed example.

Recently saved file. It opens the last file the user worked with.

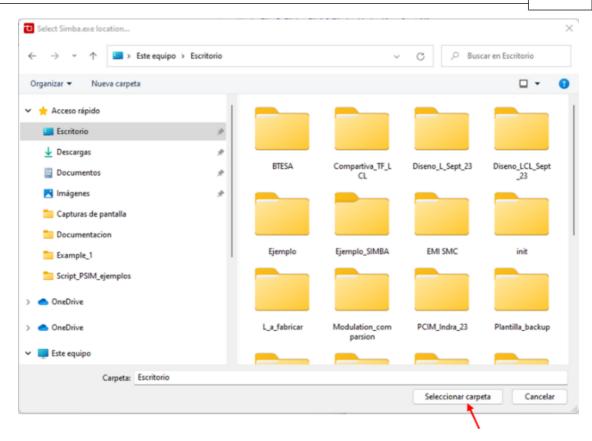

Previously saved file. It opens the folder where user used to save its designs

**Sample design.** It opens the folder where SmartCtrl examples have been previously recorded.

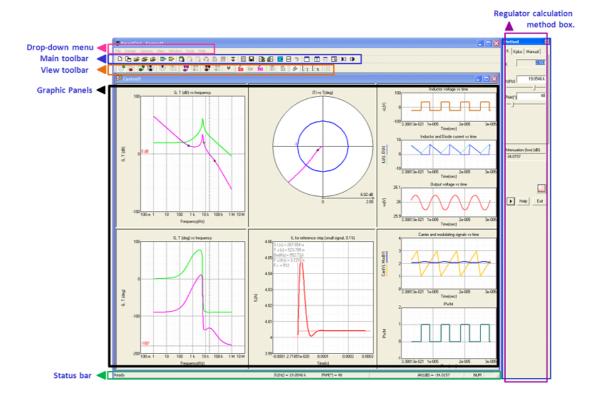

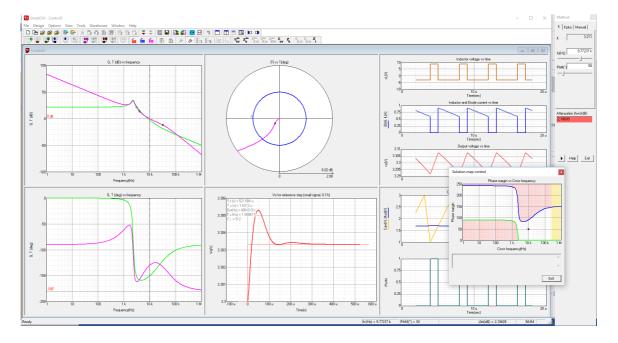

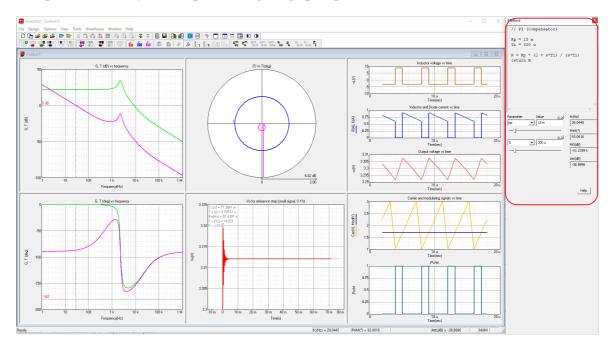

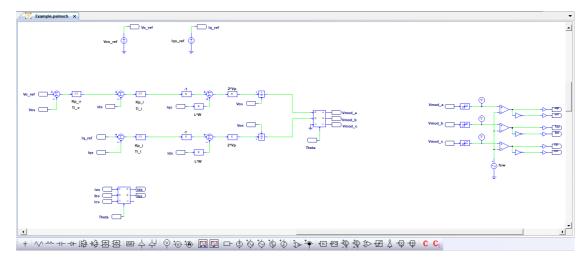

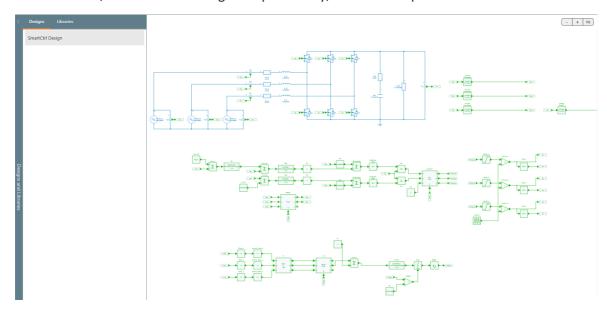

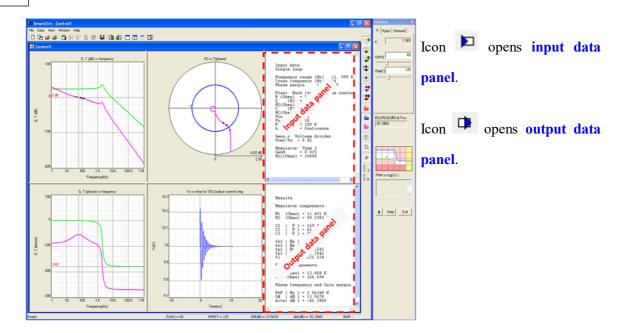

Regardless of the selected option, once the converter is completely defined, the main window of the program is displayed. Different areas are considered within the main window and all of them are briefly described below:

#### 1. There are eight drop-down menus, this is:

File It includes all the functions needed in order to manage files, import and export files, establish the printer setup and the print options.

<u>Design</u> SmartCtrl libraries, modification of input data, access to the digital control settings (only available in SmartCtrl 2.0 Pro) and parametric sweep.

**Options** For deactivating SmartCtrl licenses and check for updates

<u>View</u> Allows the user to select which elements are displayed and which are not

**Tools** Settings and Equation Editor access

**Warehouse** Components library

**Window** Functions to create, arrange and split windows

Help SmartCtrl Help

- 2. The <u>Main Toolbar</u> provides quick access to the most commonly used program functions through left click on the respective icon.

- 3. The View Toolbar icons allows the user a quick selection of the elements displayed.

- 4. The Status Bar summarizes the most important parameters of the open loop control design (cross frequency, phase margin and attenuation at the switching frequency)

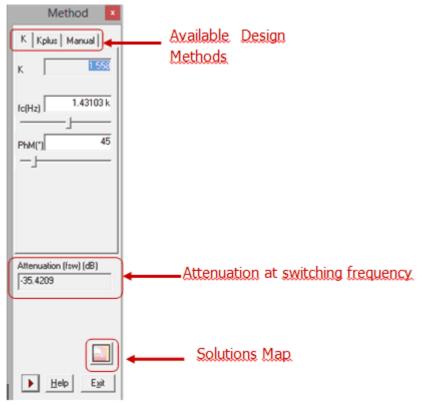

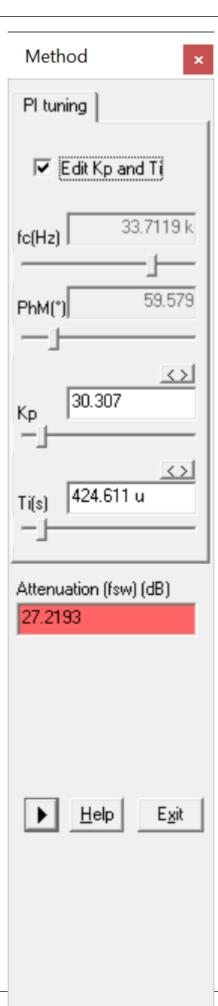

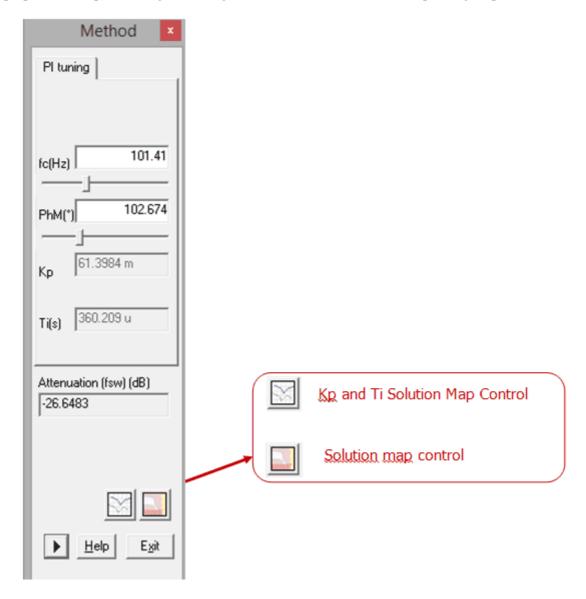

- 5. The compensator <u>Design Method Box</u> includes the three <u>calculation methods of the compensator</u> as well as the <u>Solution Map</u>.

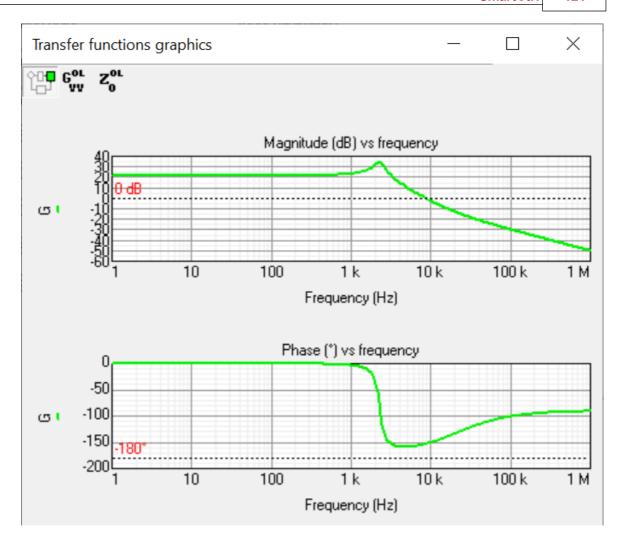

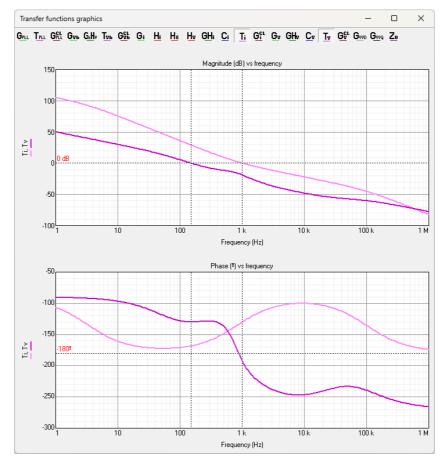

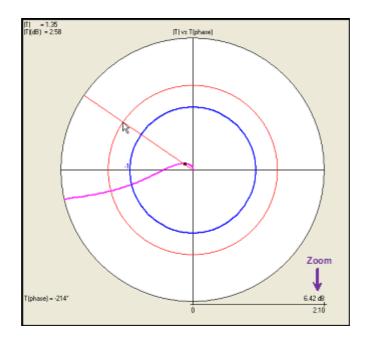

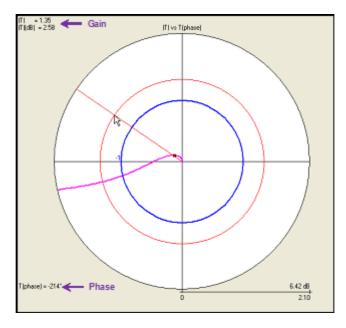

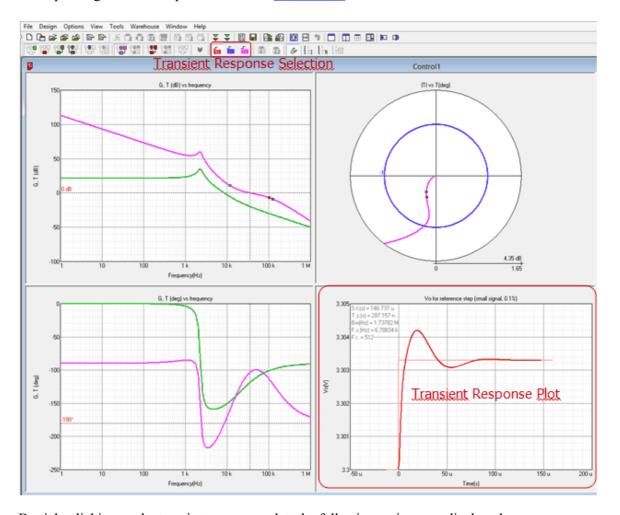

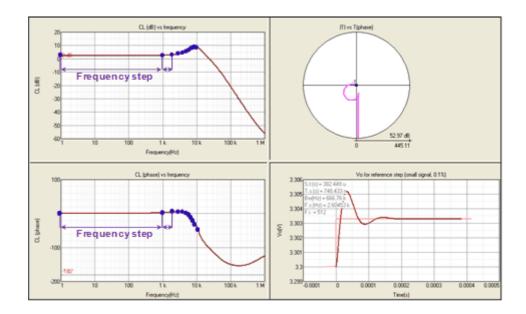

- 6. <u>Graphic and text panels</u> include the most relevant information of the system: frequency response, polar plot, transient response and steady-state waveforms. To access the help topic regarding each panel just right click on that panel.

## 1.3 Main menus and toolbars

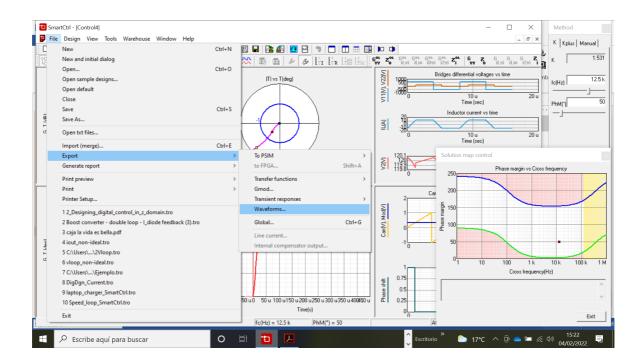

## 1.3.1 File Menu

Navigation: SmartCtrl > Main menus and toolbars >

File Menu

Previous Top Next

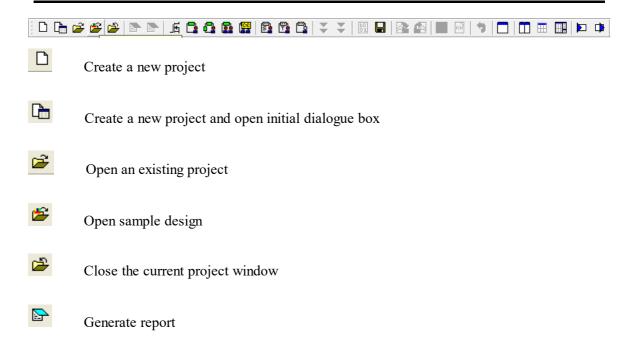

New Create a new project (Ctrl+N)

New and initial dialog Create a new project and display the initial dialog box

Open Open an existing project (Ctrl+O)

Open sample designs Open a sample design from the examples folder

Close Close the current project window

Save Save the current project (Ctrl+S)

Save as... Save the current project to a different file

Open txt files Open any .txt file in Notepad

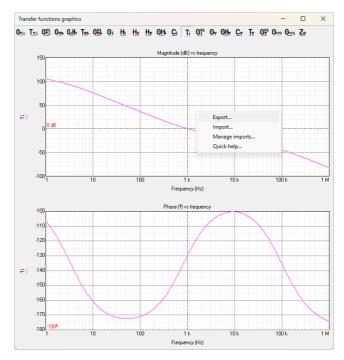

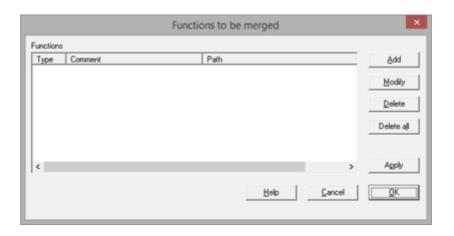

**Import (Merge)** Merge data of another file with the data of the existing file for display.

The curves of these two files will be combined. (Ctrl+M)

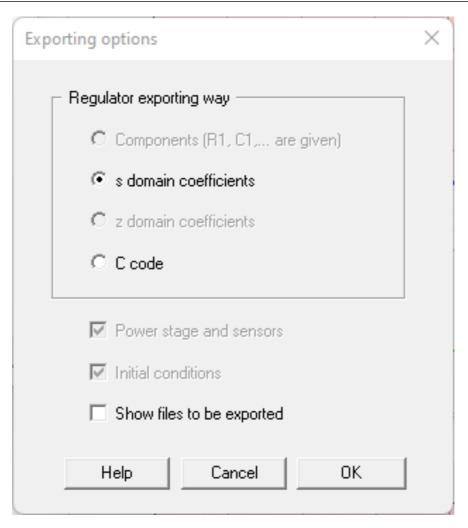

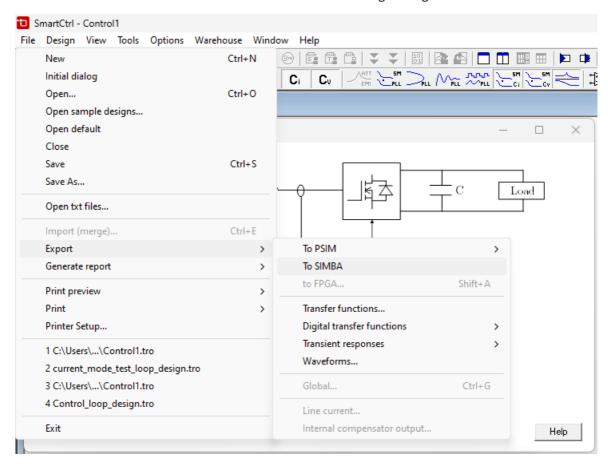

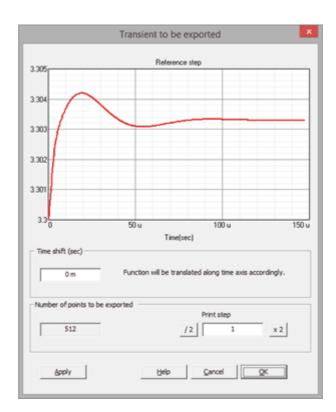

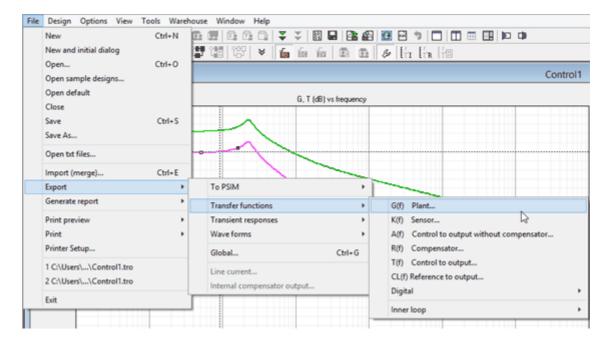

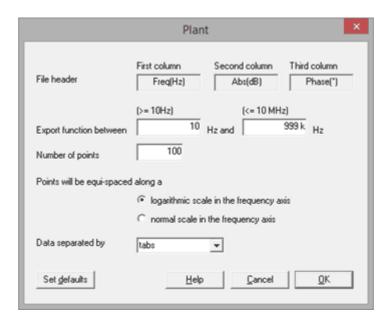

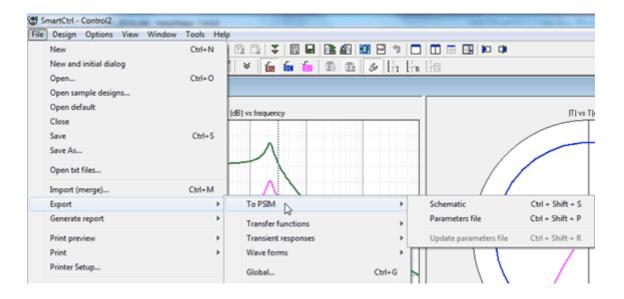

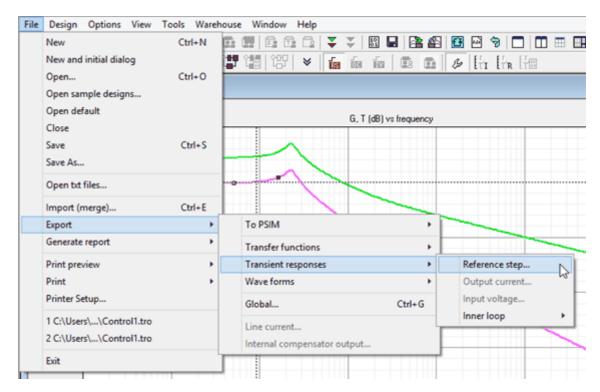

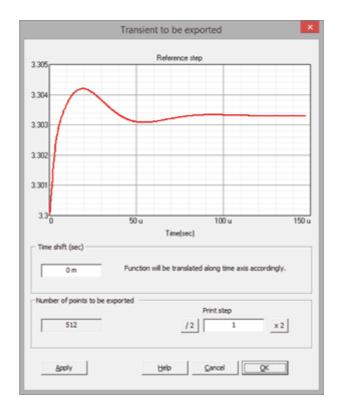

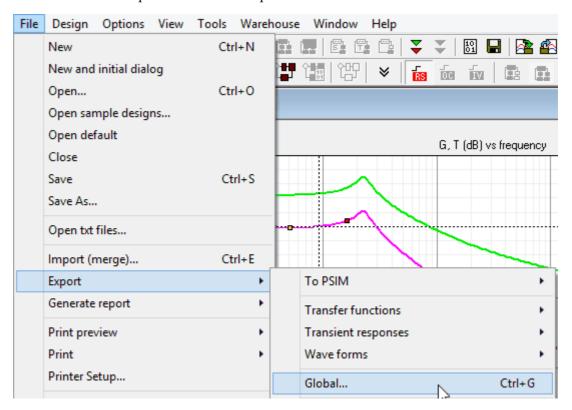

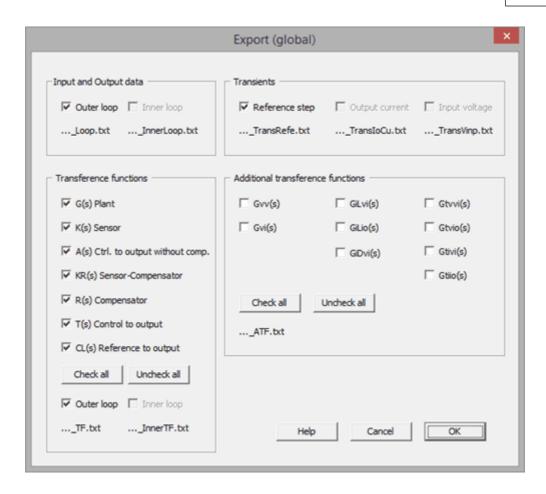

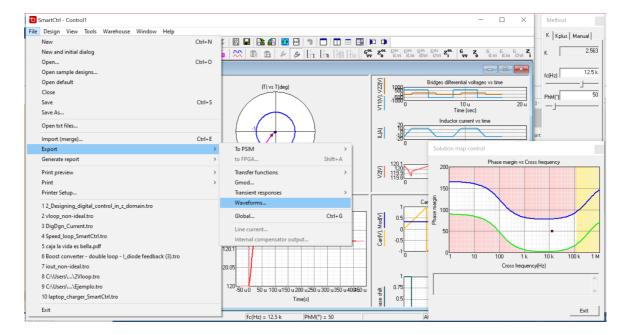

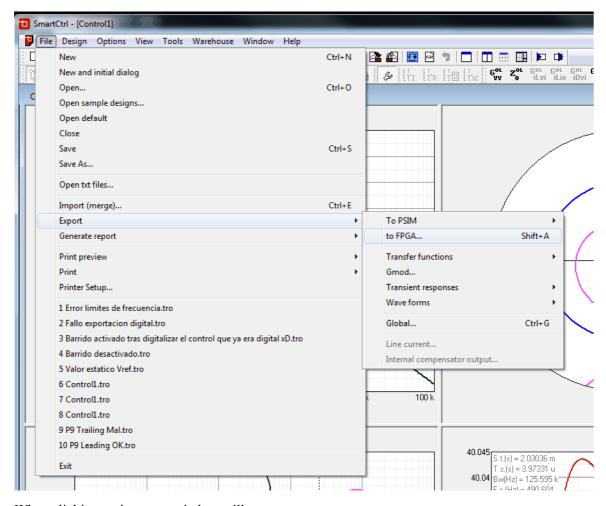

**Export** The program provides different exporting options. It allows exporting the following.

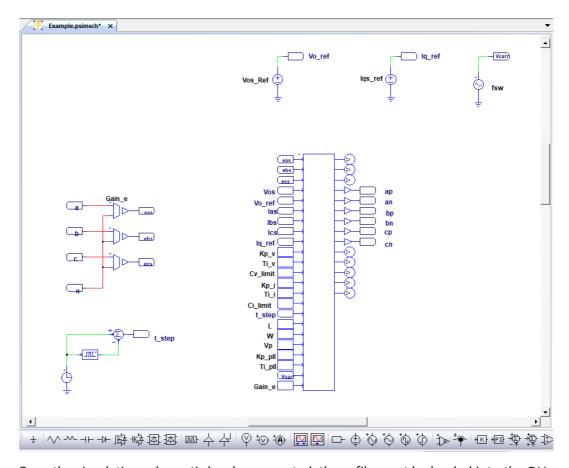

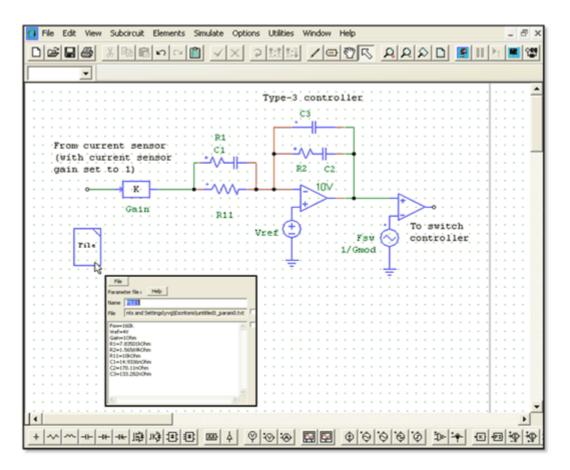

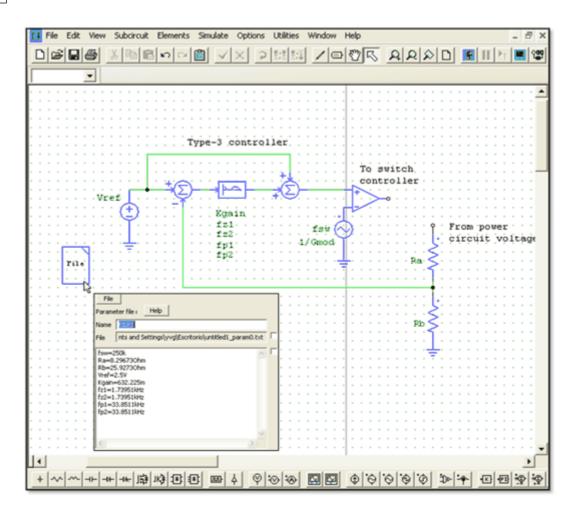

- •Export to PSIM the schematic and the parameters file, or update parameters file

- •Export to FPGA the digital compensator design (more information)

- •Export transfer functions to a file. The available transfer functions are: plant, sensor, control to output, compensator, digital, inner loop etc.

- •Export transient responses to a file. The available transient responses are: voltage reference step, output current step and input voltage step

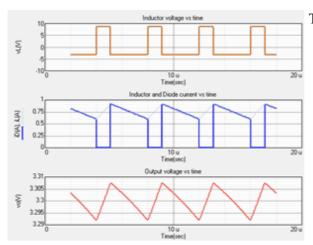

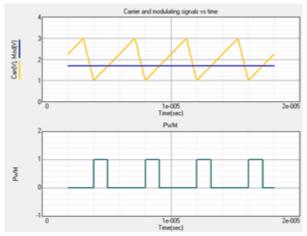

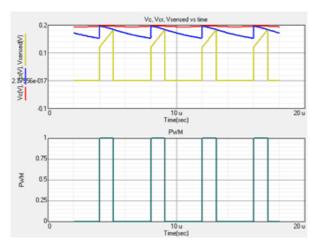

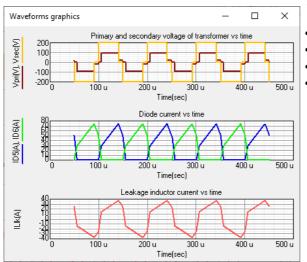

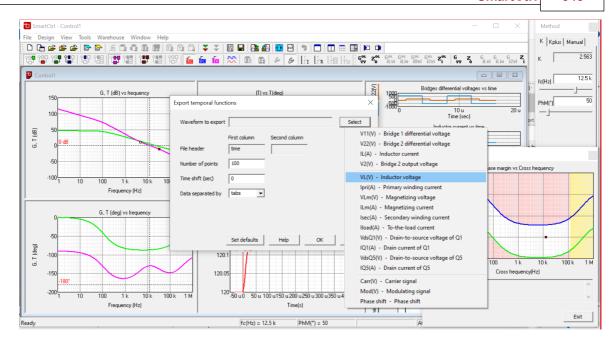

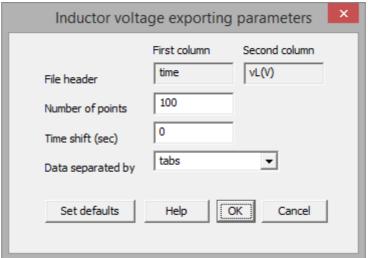

- •Export waveforms to a file. The available steady state waveforms are: inductor voltage and current, diode voltage and current, carrier, modulating signal and PWM.

Generate report Generate a report to either a .txt file or notepad. It contains information regarding both the input data (steady-state dc operating point, plant input data, ...) and output data (compensator components, cross frequency, phase margin, ...)

Print preview Preview the printout of any of the graphic and text panels (Transfer function magnitudes (dB), Transfer function phase (°), Nyquist diagram, Transients, Data input, Results)

**Print** Print any of the panels of the main window (bode plots, Nyquist diagram, transient, input data or results)

Printer setup Setup the printer

Exit Exit SmartCtrl

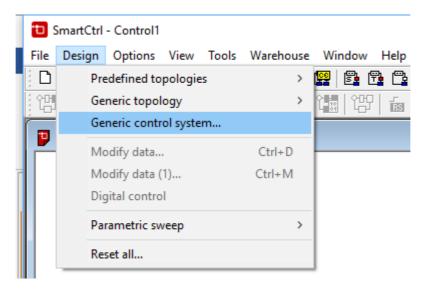

## 1.3.2 Design Menu

Navigation: SmartCtrl > Main menus and toolbars >

Design Menu

The SmartCtrl Design Menu contains the elements that can be used in the SmartCtrl schematic. The library is divided into the following sections:

<u>Predefined</u> Contains the most commonly used DC-DC plants both in single and double <u>topologies</u> loop configurations, as well as AC-DC plants.

Generic Topology Allows the user to define a generic plant transfer function either in s-domain or importing a .dat, .txt, or .fra file; uses the predefined sensors provided by SmartCtrl and, for the compensator, the user can select among the proposed types or define a compensator using the transfer function to design the closed-loop control system.

Generic Control Allows the user to define the plant and the sensor transfer functions through

System the built-in equation editor. For the compensator the user can select among the proposed types or define a compensator using the transfer function.

Modify Data Open the schematic window of the current project to modify the parameters.

<u>Digital control</u> Access to the digital control settings (only available from SmartCtrl 2.1 Pro).

<u>Parametric Sweeps</u> Allows performing the sensibility analysis of the system parameters. It is divided into three different parametric sweeps: <u>Input Parameters</u>, <a href="Compensator Components"><u>Compensator Components</u></a> and digital factors.

Reset all Clear the active window

Previous Top Next

## 1.3.3 Options Menu

Navigation: SmartCtrl > Main menus and toolbars >

## **Option Menu**

Previous Top Next

**Deactivate** When the user check the option DEACTIVATE the following message will appear:

When SmartCtrl is launched, it will contact the license server and activate the license.

For NETWORK licenses, when SmartCtrl exists it will automatically deactivate the license, and someone else can use it.

However for STAND ALONE licenses, the license will not be deactivated, it will remain active for 7 days on this computer, so considering this type of license can be used with 2 different computer IDs, it is recommendable to deactivate the license in one of them if the user is planning to use the other.

Note that activating / deactivating the license requires internet connection.

Check for software Check for a new version of SmartCtrl available

## updates...

This option will run the program SmartCtrlUpdate.exe to check if there is a new version available.

#### 1.3.4 View Menu

Navigation: SmartCtrl > Main menus and toolbars >

View Menu Previous Top Next

Comments Open the comments window. It allows the user to add comments to the design. These comments will be saved together with the designed converter.

**Loop** Select the loop to be displayed in the active window (inner or outer loop).

**Transfer Functions** Select the transfer function to be displayed:

- •Plant transfer function, G(s)

- •Sensor transfer function, K(s)

- •Compensator transfer function, R(s)

- •Control to output without regulator transfer function, A(s)

- •Control to output transfer function, T(s)

- •Reference to output transfer function, CL(s)

- •Digital compensator transfer function

- •Digital control to output transfer function

- •Digital reference to output transfer function

**Additional transfer** Select the additional transfer functions to be displayed, like the **functions** audiosusceptibility Gvv, the output impedance Gvi, etc. For more information regarding these transfer function, see <u>view toolbar</u>.

**Transients** Select the transient response to be displayed.

The available transient responses are:

- •Input voltage step transient

- •Output current step transient

- •Reference step transient.

Organize panels Resize all panels and restore the default appearance of the graphic and results panels window.

**Enhance** Select the panel to be displayed in full screen size

| <ul><li>Bode (magnitudes) panel</li></ul> | (Ctrl+Shift+U) |

|-------------------------------------------|----------------|

| •Bode (phase) panel                       | (Ctrl+Shift+J) |

| <ul> <li>Nyquist diagram panel</li> </ul> | (Ctrl+Shift+I) |

| •Transient responses panel                | (Ctrl+Shift+K) |

| •Input data panel                         | (Ctrl+Shift+O) |

| <ul><li>Output (results) panel</li></ul>  | (Ctrl+Shift+L) |

Input data View design input data

Output data View design output data

## 1.3.5 Tools Menu

Navigation: SmartCtrl > Main menus and toolbars >

Tools Menu Previous Top Next

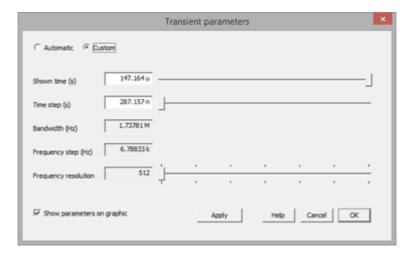

**Settings** It allows the customization of the frequency range (<u>frequency settings</u>) and the default re-arrangement of the graphic and text panels to their default size and appearance (<u>Layout settings</u>)

Equation editor The equation editor provides direct access to the SmartCtrl built-in Equation editor. Through the Equations ditor, SmartCtrl allows the user to program any transfer function, export its frequency response and afterwards, if needed, import and visualize it within the Bode plots graphic panel

#### 1.3.6 Warehouse Menu

Navigation: SmartCtrl > Main menus and toolbars >

#### Warehouse Menu

Previous Top Next

SmartCtrl provides a wide selection of different components used in the design of power circuits, called warehouse. This database is available through the next button:

For more information: Warehouse

#### 1.3.7 Window Menu

Navigation: SmartCtrl > Main menus and toolbars >

## Window Menu

Previous Top Next

**New Window** Create a new window

Maximize active window Maximize the current window

Cascade Arrange the windows in cascade form

Tile horizontal Tile the currently open windows horizontally

Tile vertical Tile the currently open windows vertically

**Split** Click on the intersection of the lines that delimit the different window panels and drag. This will change the size of the panels

Organize all It restores the default size of the graphic and text panels

.

## 1.3.8 Help Menu

Navigation: SmartCtrl > Main menus and toolbars >

## Help Menu

Previous Top Next

What's new in this New features included in the last SmartCtrl version

version

**Contents** Help file

About SmartCtrl... SmartCtrl information

## 1.3.9 Main toolbar

Navigation: SmartCtrl > Main menus and toolbars >

Main toolbar Previous Top Next

**2**

锤

Save the current project

Export transfer functions

Export to PSIM (schematics)

Import transfer function from a file and merge with other Transfer Functions

- Export to PSIM (update parameter file)

Update parameters file of the previously exported schematic

- Maximize active window

- Tile windows

- See all panels

- Organize all panels

- View input data

- View output data

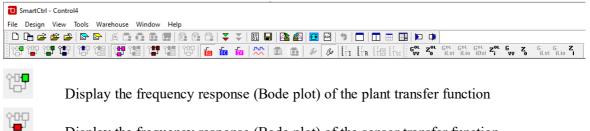

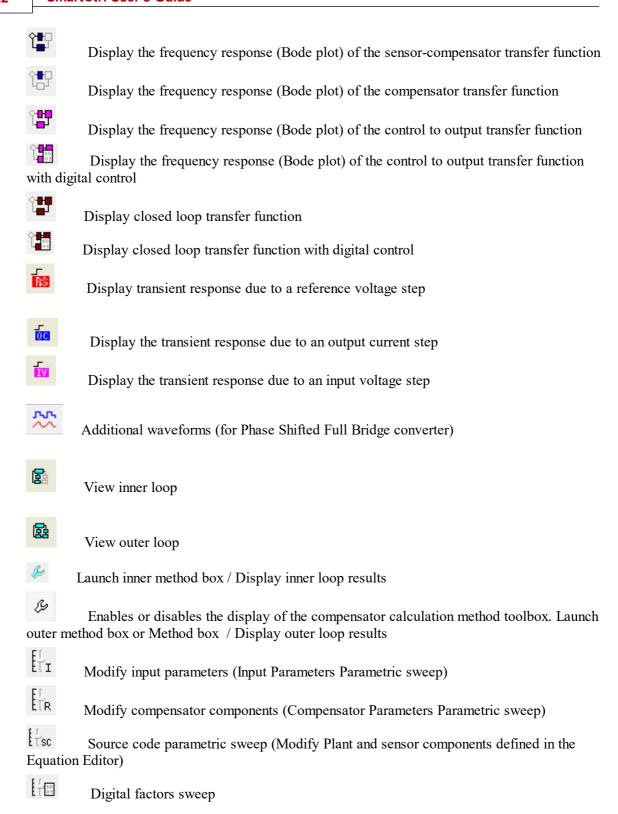

## 1.3.10 View toolbar

Navigation: SmartCtrl > Main menus and toolbars >

View toolbar

Previous Top Next

Display the frequency response (Bode plot) of the sensor transfer function

Display the frequency response (Bode plot) of the control to output without compensator transfer function

#### SmartCtrl additional transfer functions

All those transfer functions colored in grey are not allowed for the design. The nomenclature of the transfer functions is as follows:

| 1 | Subscript 1 refers to the type of transfer function studied. The character t denotes that the transfer function has been evaluated in closed loop; otherwise it refers to open loop. |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | <ul> <li>Subscript 2 refers to the perturbed magnitude:</li> <li>iL: inductor current.</li> <li>iD: diode current.</li> </ul>                                                        |

| 3 | <ul> <li>vo: output voltage</li> <li>Subscript 3 refers to the perturbing magnitude:</li> <li>io: output current.</li> <li>vi: input voltage.</li> </ul>                             |

|   |                                                                                                                                                                                      |

The considered transfer functions are:

Open loop transfer functions.

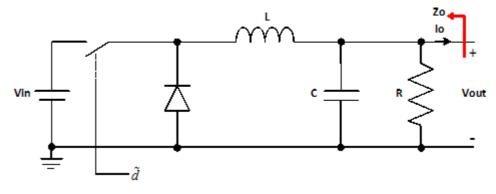

| $Gvvi = \frac{\tilde{v}_o}{\tilde{v}_i}$          | Open loop Audiosusceptibility                                                     |  |

|---------------------------------------------------|-----------------------------------------------------------------------------------|--|

| $Gvio = \frac{\tilde{v}_o}{\tilde{i}_o}$          | Open loop Output impedance                                                        |  |

| $GiLvi = \frac{\tilde{i}_L}{\tilde{v}_i}$         | Open loop Input voltage to inductor current transfer function.                    |  |

| $GiLio = \frac{\tilde{i}_L}{\tilde{i}_o}$         | Open loop Output current to inductor current transfer function.                   |  |

| $GiDvi = \frac{\tilde{i}_D}{\tilde{v}_i}$         | Open loop Input voltage to diode current transfer function.                       |  |

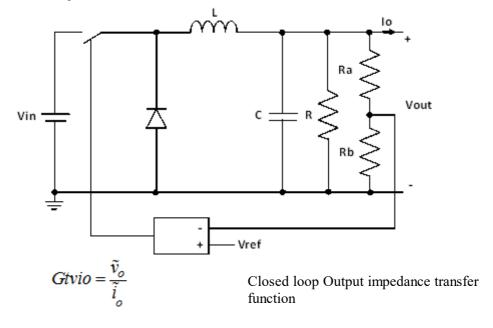

| Closed loop transfer functions.                   |                                                                                   |  |

| $Gtvvi = \frac{\widetilde{v}_o}{\widetilde{v}_i}$ | Closed loop Audiosusceptibility                                                   |  |

| $Gtvio = \frac{\tilde{v}_o}{\tilde{i}_o}$         | Closed loop Output impedance                                                      |  |

| Gtivi                                             | Closed loop Input voltage to inductor current or diode current transfer function  |  |

| Gtiio                                             | Closed loop Output current to inductor current or diode current transfer function |  |

The nomenclature will be clarified through two examples.

Example 1: Open loop transfer function.

$$Gvio = \frac{\tilde{v}_o}{\tilde{l}_o}$$

Load resistor is included within the output impedance transfer function

Example 2: Closed loop transfer function.

# 1.4 Design a predefined topology

Navigation: SmartCtrl >

## Design a predefined topology

Previous Top Next

The most widely used topologies are available as pre-defined topologies, in order to ease their design.

The available pre-designed topologies are:

- •DC-DC power stage and control design.

- •DC-DC converter Single loop (Voltage mode control and current mode Control).

- •DC-DC converter Peak current mode control.

- •DC-DC converter Average current mode control.

- •PFC Boost converter

## 1.4.1 DC-DC power stage and control design

Navigation: SmartCtrl > Design a predefined topology >

DC-DC power stage and control design

Previous Top Next

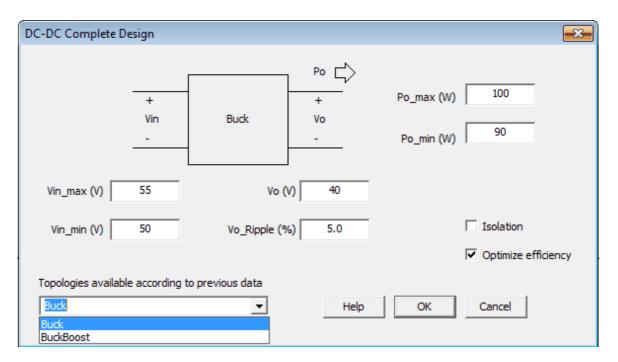

If this option is selected, SmartCtrl helps to design a complete DC-DC converter (plant, sensor and controller) from simple specifications.

Predefined topologies for this option are:

- •Buck

- •Boost

- •Buck-boost

- Forward

- •Flyback

All these topologies are designed for a Continuous Conduction Mode (CCM), and a simple Voltage Control Mode (VCM).

The first step is to specify the characteristics of the circuit. These are:

- •Input voltage range (maximum and minimum)

- Output voltage

- •Maximum output voltage ripple

- •Ouput power range

If desired, the check box Isolation"can be selected to use a topology with isolation (Forward or Flyback).

SmartCtrl determines the available topologies for these specifications. Once a topology has been selected, click on Ok button.

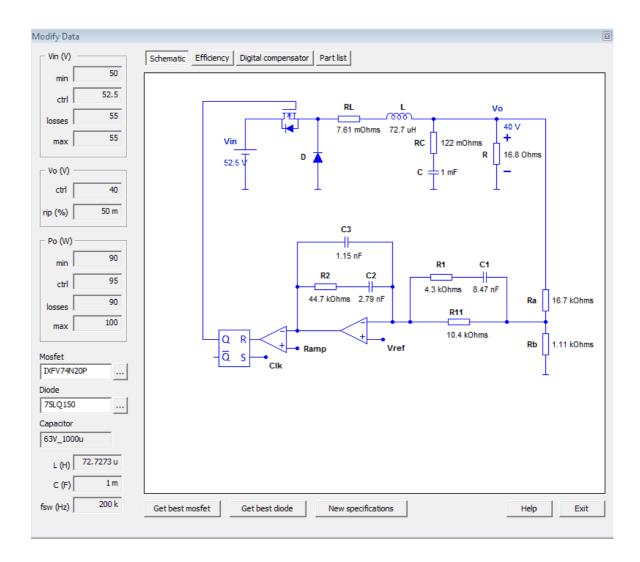

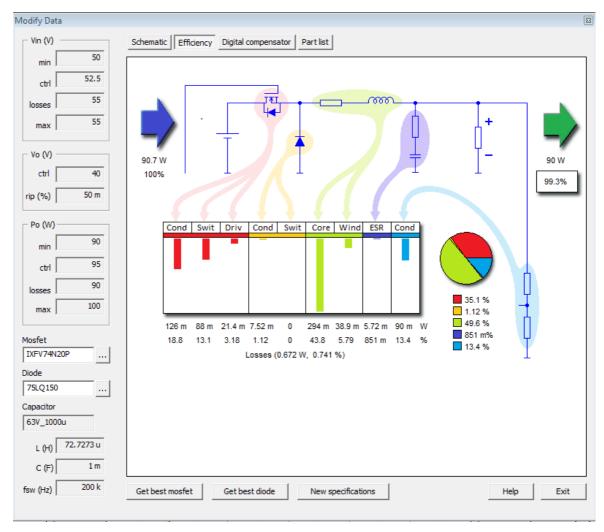

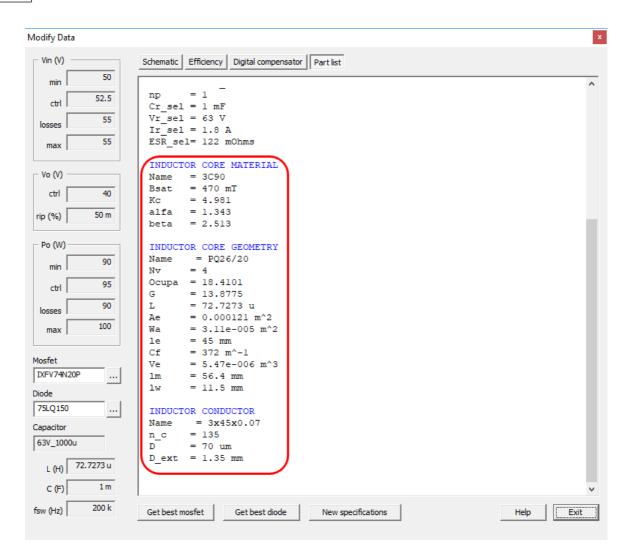

After that, a new window is shown with four tabs:

- Schematic

- Efficiency

- •Digital compensator

- Part list

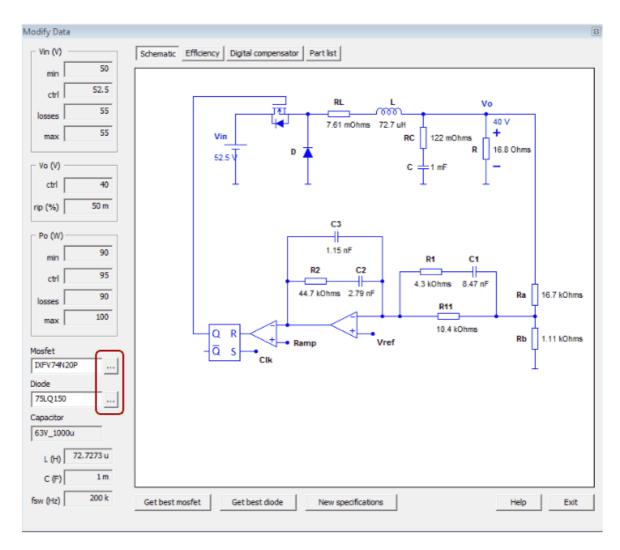

In the tab **Schematic**,"the complete circuit is shown, including sensor and regulator. All values are detailed on each component.

If the tab **Efficiency**'s selected, the information about the loses in each component is shown.

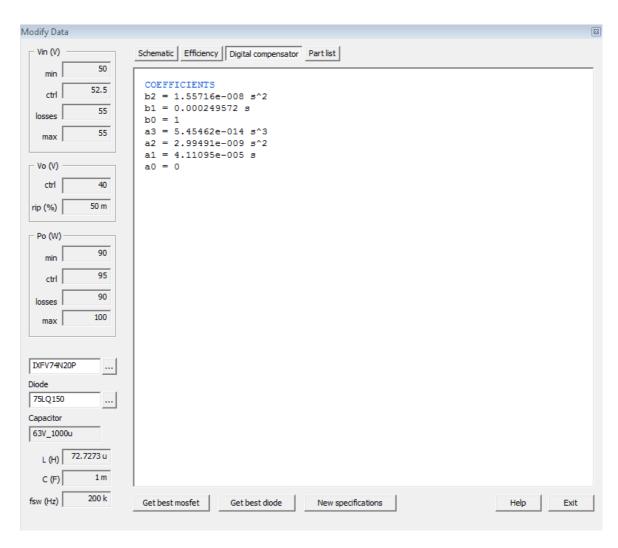

In the tab **Digital compensator**'the coefficients for a digital control are shown.

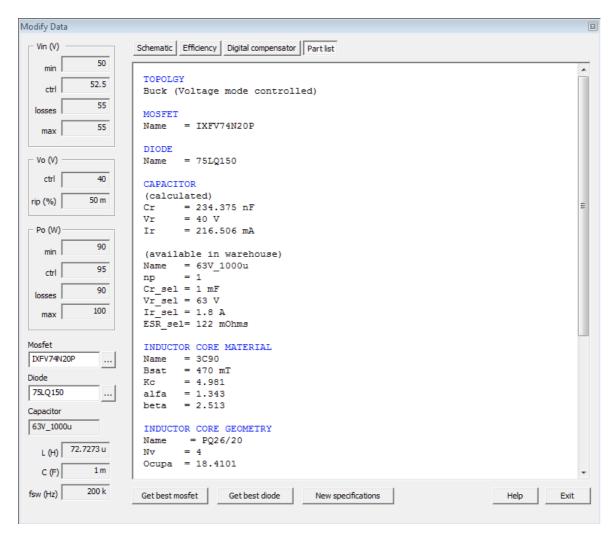

In the tab **Part list**'there is a list with the components from the warehouse selected for the optimum design.

In any of these tabs, it is possible to change the selected diode and MOSFET between the available ones in the warehouse by clicking in the buttons marked in the next picture:

In this part list the user also gets information about how to build the **inductor** used in the design, with complete details about the core material, core geometry and wire and number of turns.

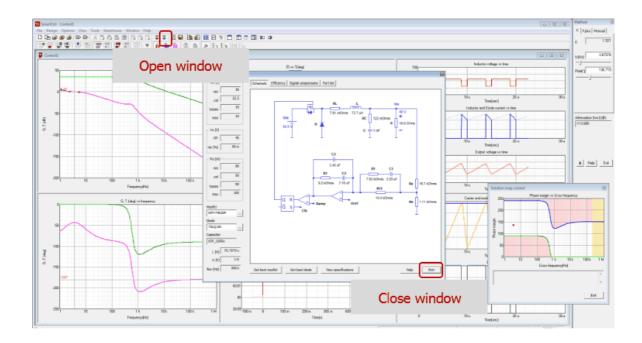

Once the system has been defined, the designer can select a point within the solution space. The variations of this design will be updated automatically in the solutions window.

The window with the results off the design can be closed and opened by clicking in the buttons marked in the next picture:

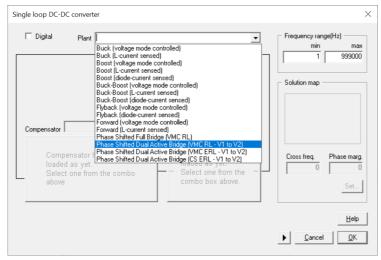

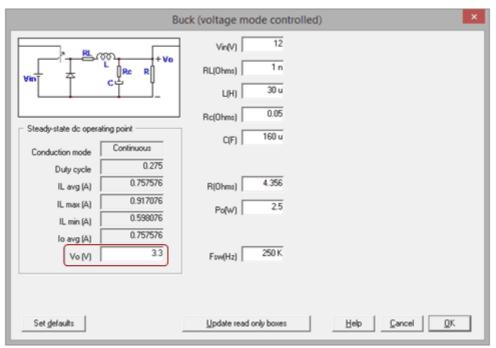

## 1.4.2 DC-DC Converter - Single loop

Navigation: SmartCtrl > Design a predefined topology >

## **DC-DC Converter - Single Loop**

Previous Top Next

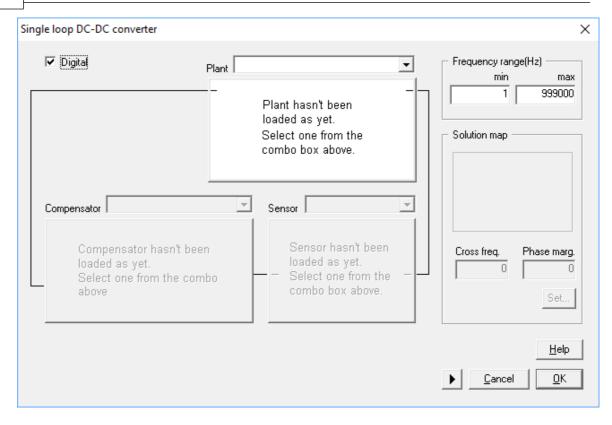

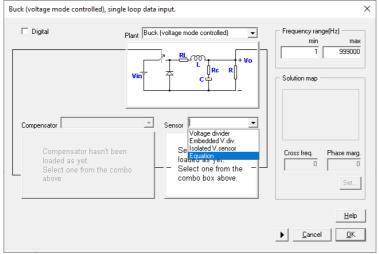

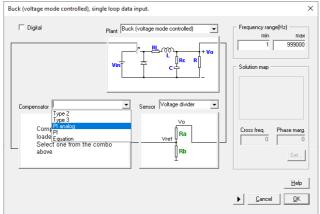

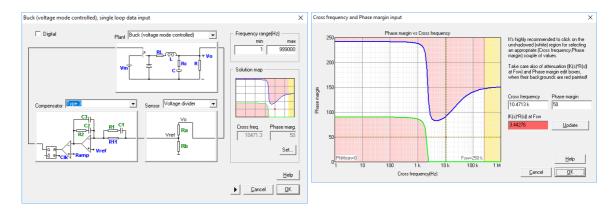

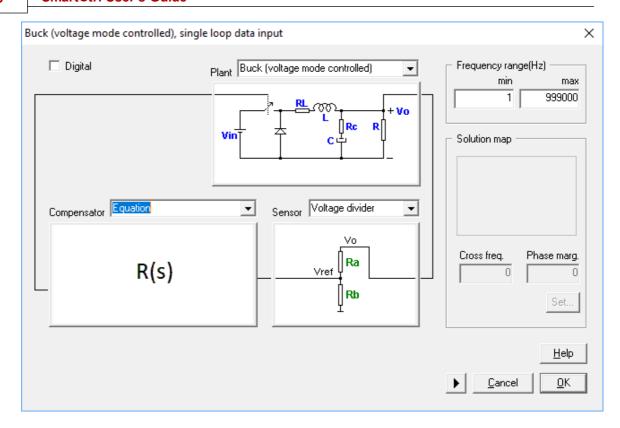

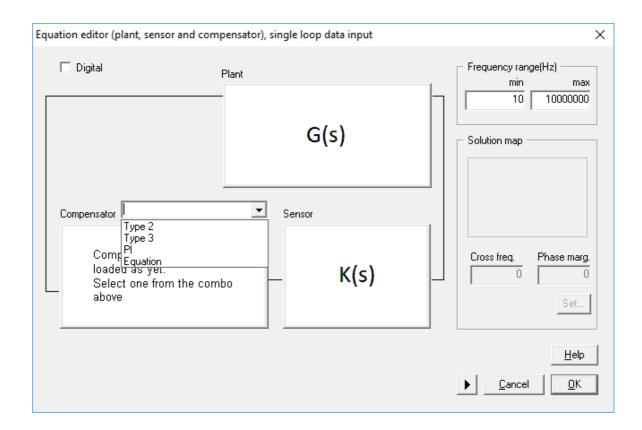

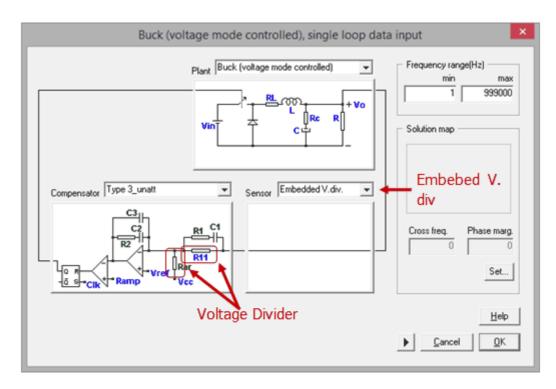

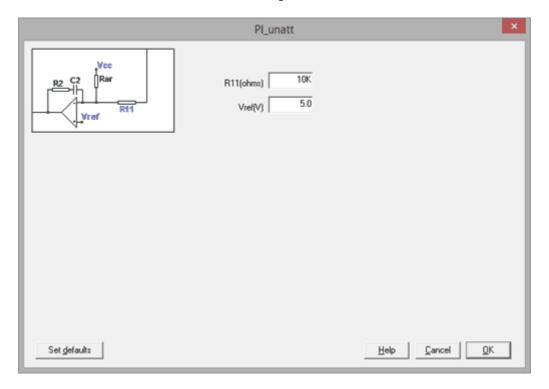

The single loop is formed by three different transfer functions: plant, sensor and compensator, which must be selected sequentially.

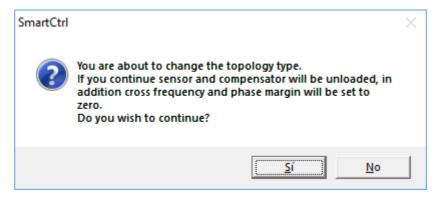

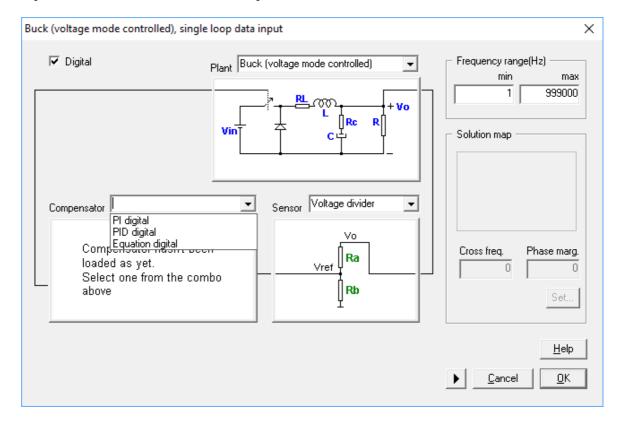

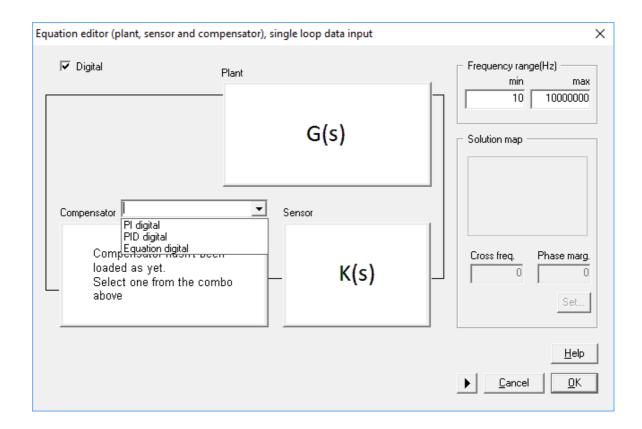

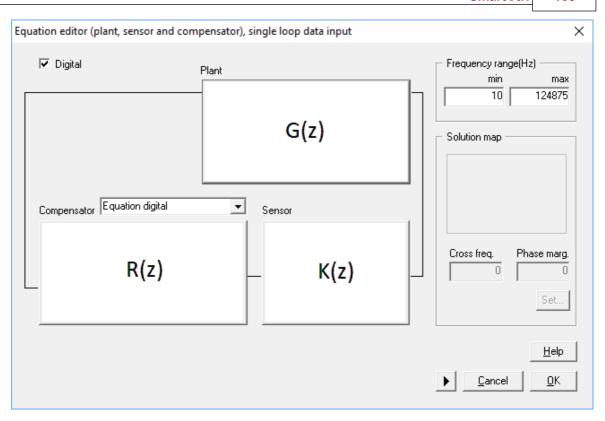

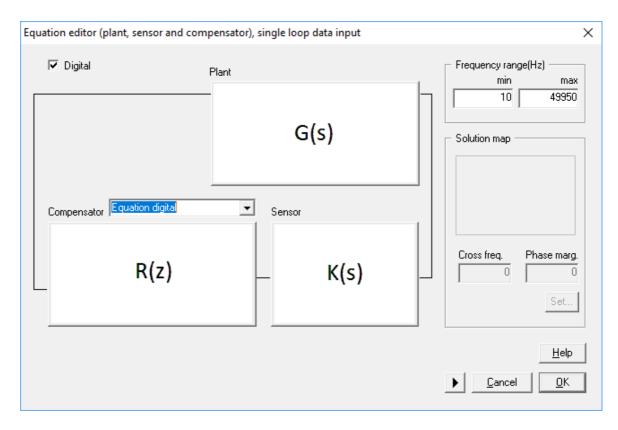

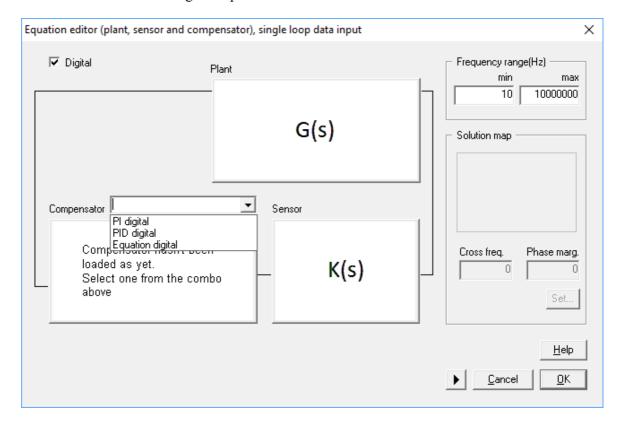

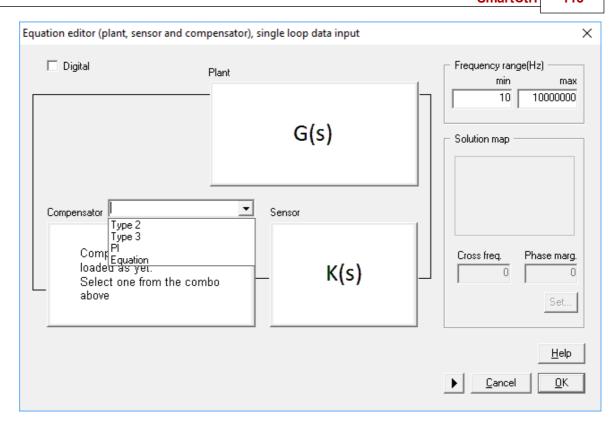

First of all the user should decide if is going to define a **digital control or an analog control**. This check box should be selected since the beginning because it determines the different options that can be selected further on.

In case this check box is modified during the design process, the user will receive an error message and it will start again in the single loop DC-DC converter window.

For both options, analog or digital control, the user should follow the same steps.

The first step is to define the system is the selection of the plant. The plant can be either a predefined one or a user defined one. This is, the user can <u>import a generic transfer function</u> by means of a .txt file or select one of the pre-defined topologies.

The predefined DC-DC plants are the following:

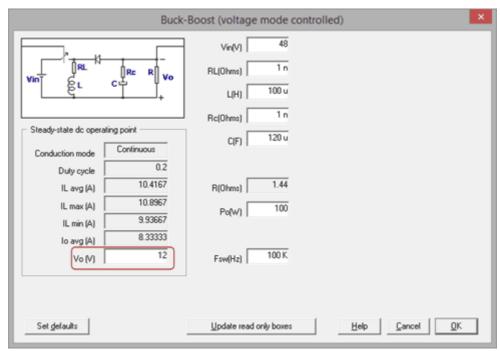

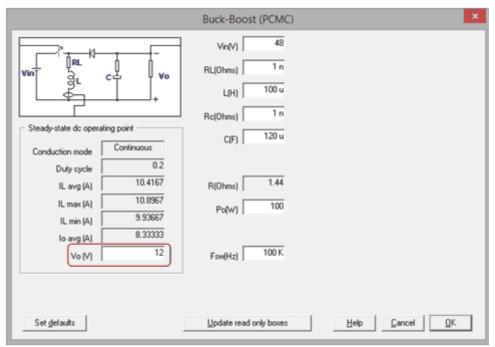

- Buck

- Buck-Boost

- Boost

- Flyback

- •Forward

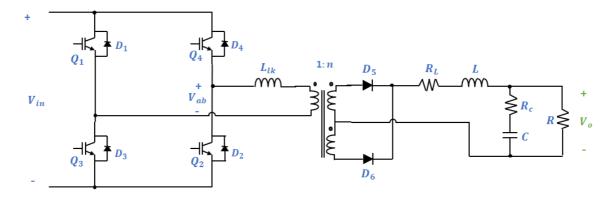

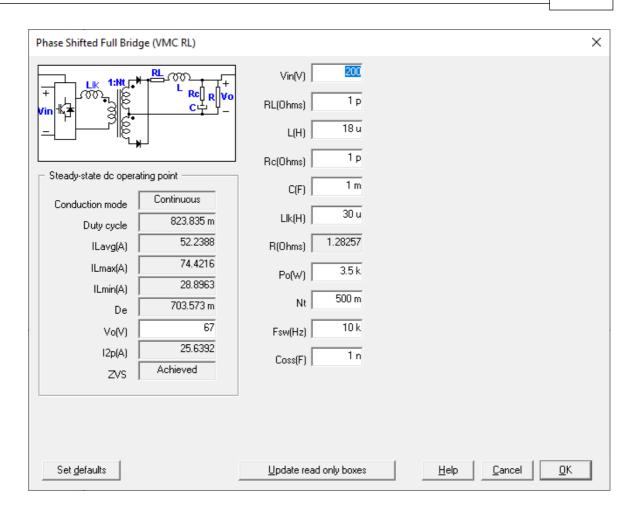

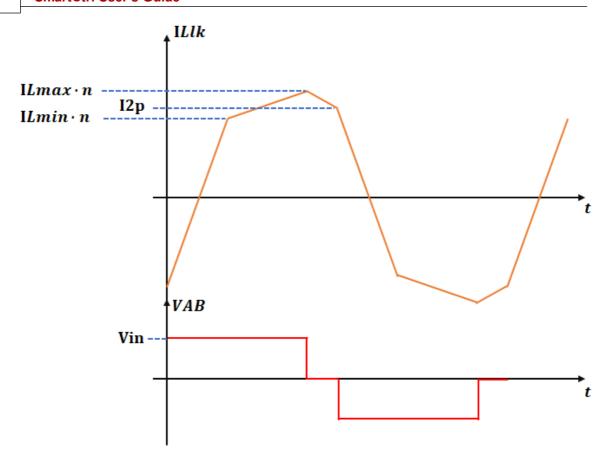

- •Phase Shifted Full

**Bridge (VMC RL)**

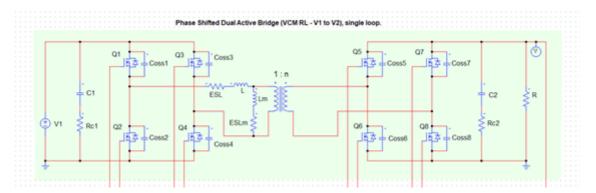

- Phase Shifted Dual Active Bridge (VMC RL

- V1 to V2)

- Phase Shifted Dual

- **Active Bridge (VMC)**

- **ERL V1 to V2**)

- •Phase Shifted Dual

- **Active Bridge (CS ERL**

- V1 to V2)

Once the plant has been selected, considering if the magnitude to be controlled is voltage or current and if the control is analog or digital, the program will display the appropriate type of sensor.

The different sensors available are the following:

- Voltage Divider

- Embedded Voltage Divider

- Isolated Voltage Sensor

- Current Sensor

- Hall Effect Sensor

- Equation Editor (User Defined Sensor)

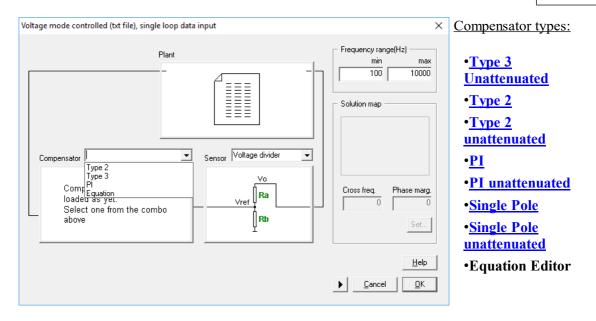

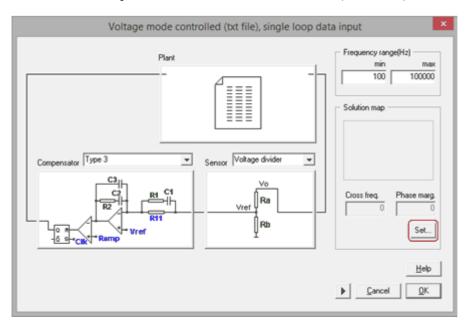

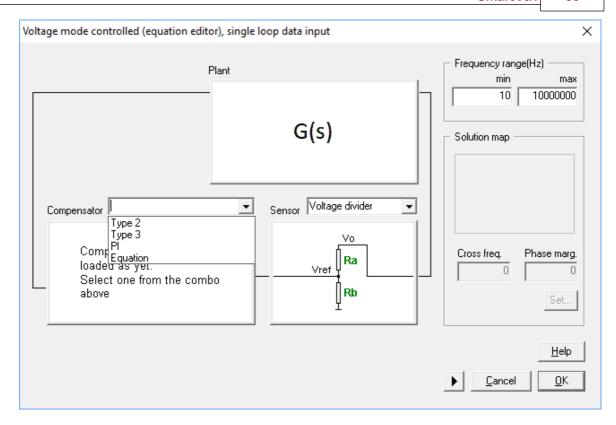

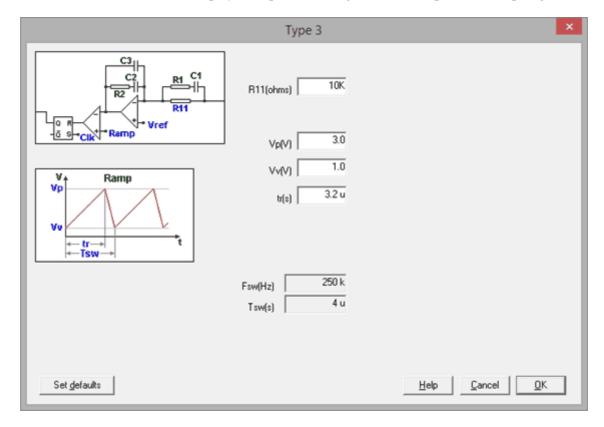

Finally, the compensator is selected, considering the suitable compensator according to the predefined DC-DC plant selected and if the design is digital or analog.

The user can select among the ones provided by SmartCtrl or use the Equation Editor to define the compensator transfer function:

Compensator types:

- <u>Type 3</u>

- Type 3 Unattenuated (when selecting Embedded Voltage Divider sensor)

- <u>Type 2</u>

- Type 2 unattenuated (when selecting Embedded Voltage Divider sensor)

- <u>PI</u>

- •PI analog

- <u>PI unattenuated</u> (when selecting Embedded Voltage Divider sensor)

- Single Pole

- <u>Single Pole unattenuated</u> (when selecting Embedded Voltage Divider sensor)

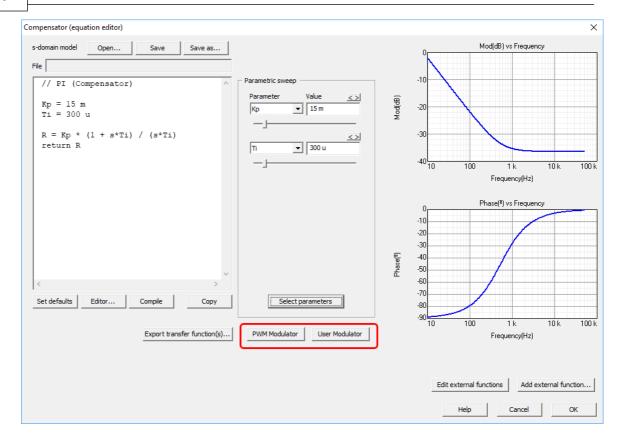

- •User defined compensator using **Equation Editor**

In case a digital control is selected from the beginning, only the digital compensators or the Equation Editor for custom defined compensator, will be available.

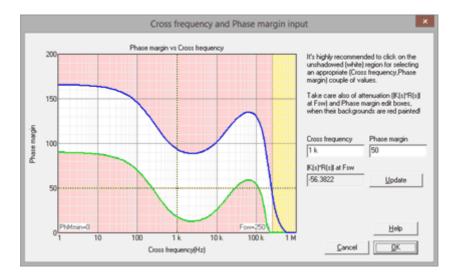

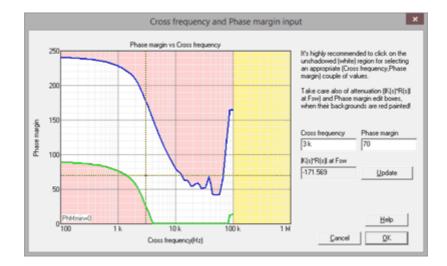

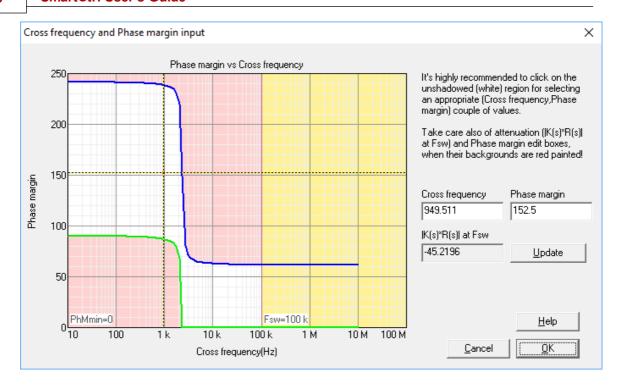

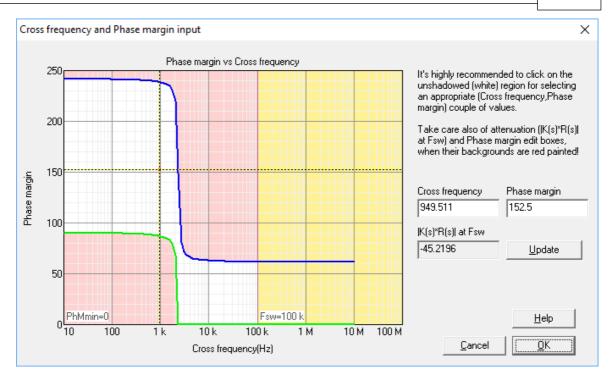

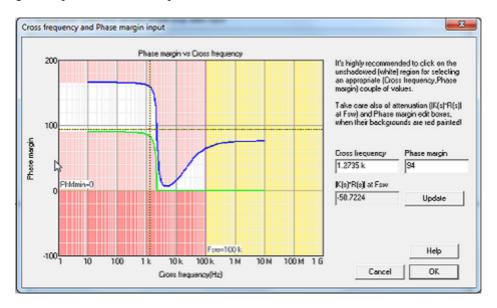

Once the system has been defined, SmartCtrl calculates the stable solution space in which all the possible combinations of crossover frequency and phase margin that lead to stable solutions are shown graphically. It is called <u>Solutions Map</u>. This option is available only for pre-defined compensators.

The designer is asked to select a point within the solution space to continue. To do that, just click on Set and select a point within the white zone.

Now accept the selected point and confirm the design, the program will automatically show the performance of the system in terms of frequency response, transient response... (See <u>Graphic and text panels window</u> for detailed information)

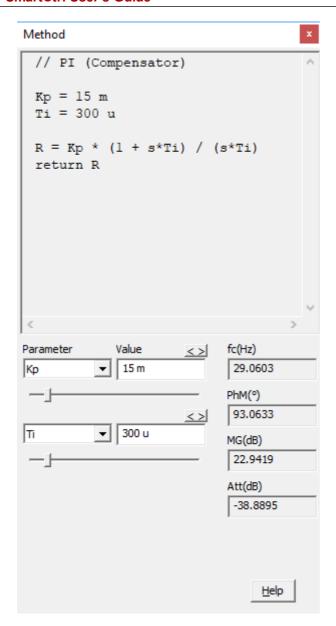

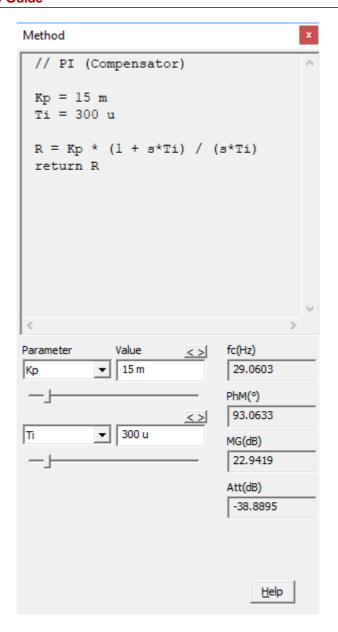

When the compensator has been defined using the Equation Editor, the solutions map is not available.

Instead of using the solutions map a Method box will appear with the compensator parameter sweep to check the system response using the graphic panels.

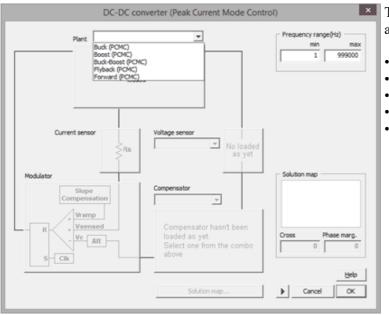

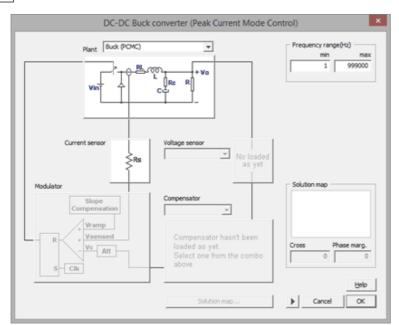

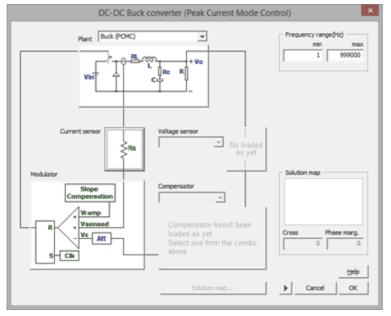

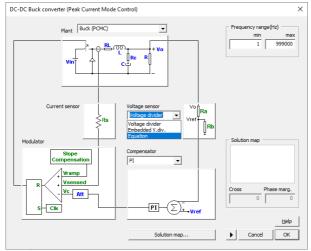

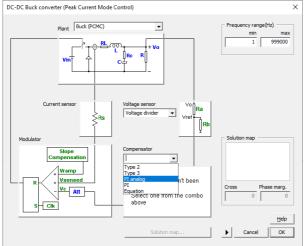

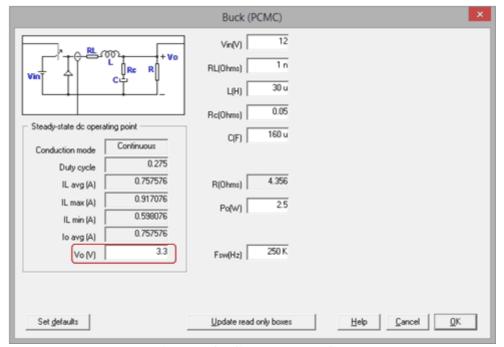

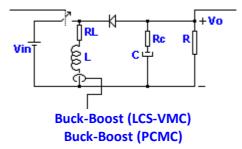

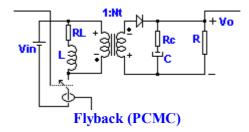

## 1.4.3 DC-DC Converter - Peak Current Mode Control

Navigation: SmartCtrl > Design a predefined topology >

## DC-DC Converter - Peak Current Mode Control

Previous Top Next

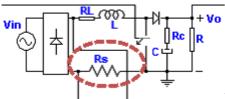

The implementation of the peak current mode control includes five different elements which are described along the following paragraphs:

- •DC-DC converter (pre-defined topologies).

- •Current sensor (implemented by means of a resistor).

- •Modulator.

- •Voltage sensor.

- •Compensator.

The program will guide you through the parameterization of the different elements, which must be carried out sequentially.

The first step to define the system is to select the plant from an existing library.

The predefined DC-DC plants are the following:

- •Buck

- Buck-Boost

- •Boost

- Flyback

- Forward

Once the plant has been selected, the value of the resistor that implements the current sensor must be set.

Current sensor available:

• Resistor

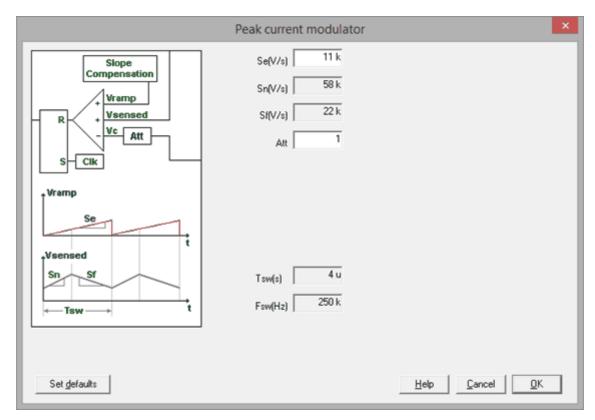

Next, the modulator must be configured.

Modulators available:

• Modulator (Peak Current Mode Control).

Right after the selection of the modulator, the voltage sensor must be selected.

Voltage sensor available:

- •Voltage divider.

- Embedded Voltage Divider

- Equation Editor (User Defined Sensor)

The last element that must be set is the compensator.

Compensator types:

- <u>Type 3</u>

- •<u>Type 3 Unattenuated</u> (when selecting Embedded Voltage Divider sensor)

- <u>Type 2</u>

- Type 2 unattenuated (when selecting Embedded Voltage Divider sensor)

- •PI analog

- •**PI**

- •PI unattenuated (when selecting Embedded Voltage Divider sensor)

- •User defined compensator using **Equation Editor**

The user must select the control loop initial characteristics (cross frequency and phase margin), aided by the <u>Solutions Map</u> (only for pre-defined compensators). After that, click OK and the program will automatically show the graphics panels.

In case the user has selected a customized compensator using the equation editor, use the compensator parameter sweep available in the Method box.

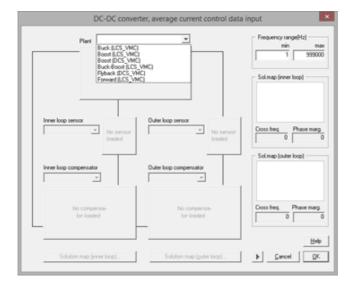

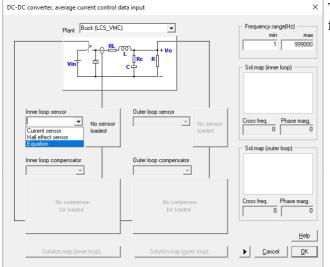

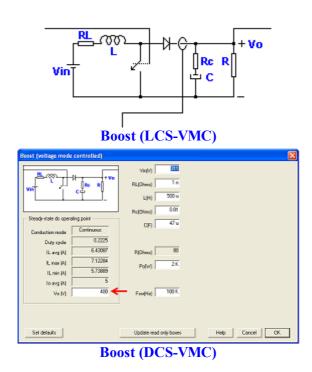

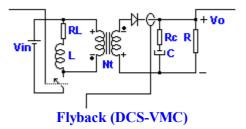

## 1.4.4 DC-DC Converter - Average Current Control

Navigation: SmartCtrl > <u>Design a predefined topology</u> >

# **DC-DC Converter - Average Current Control**

Previous Top Next

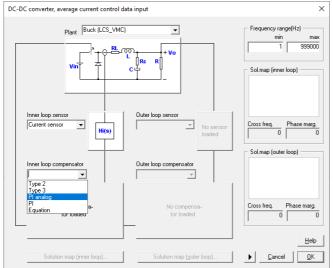

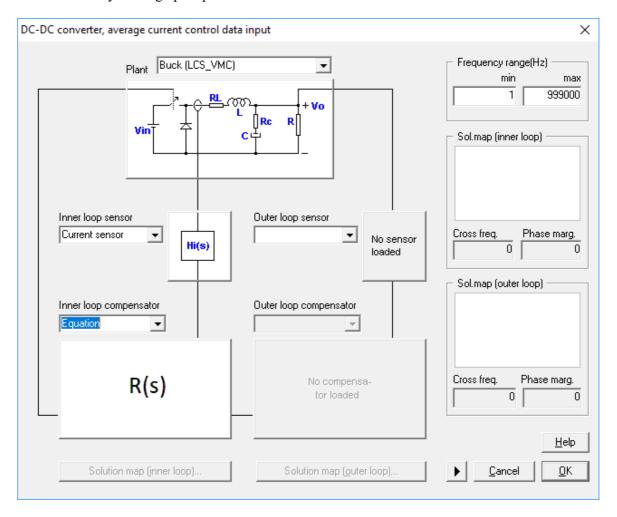

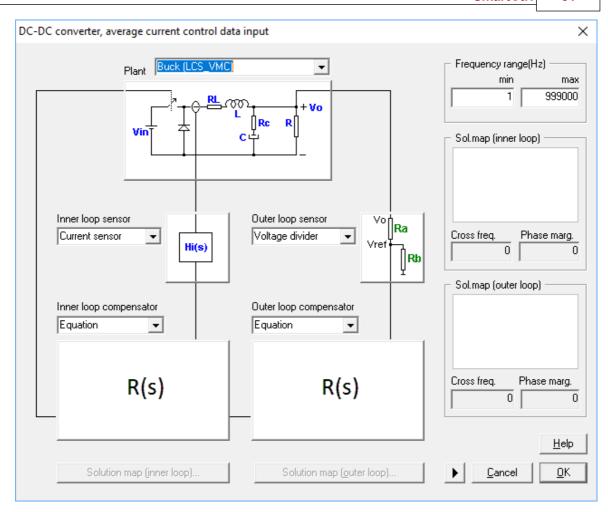

The average current control is composed by an inner current loop and an outer voltage mode loop. Same as the single loop, the double loop setup must be built sequentially. The program will guide you to build it, enabling the following step and keeping everything else disabled.

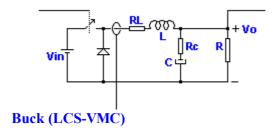

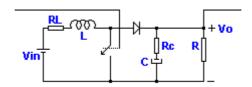

In all the available plants, the outer loop is a voltage mode control (VMC), while the inner loop is a current controlled one. Depending on the selected plant, the current is sensed either on the inductance (LCS) or on the diode (DCS). The DC-DC plant must be selected among the following list

The predefined DC-DC plants are the following:

- •Buck (LCD-VMC)

- •Buck-Boost (LCS-VMC)

- •Boost (LCS-VMC)

- Boost (DCS-VMC)

- Flyback (DCS-VMC)

- Forward (LCS-VMC)

Next, the inner control loop will be configured. This is, the current sensor and the regulator type must be selected.

The available current sensors are the following:

- •Current Sensor

- Hall Effect Sensor

- <u>Equation Editor (User Defined Sensor)</u>

Finally, the inner loop compensator is selected.

Compensator types:

- <u>Type 3</u>

- **Type 2**

- •PI analog

- •<u>PI</u>

- •Single Pole

- •User defined compensator using **Equation Editor**

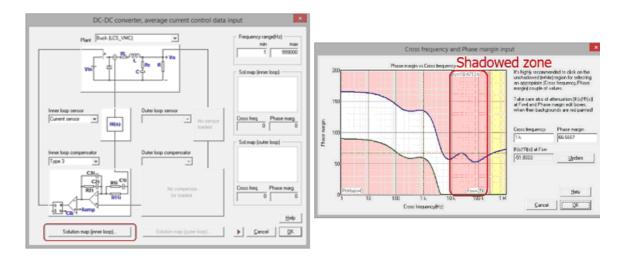

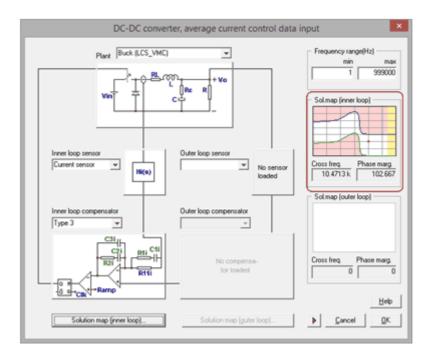

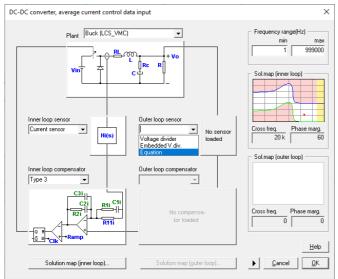

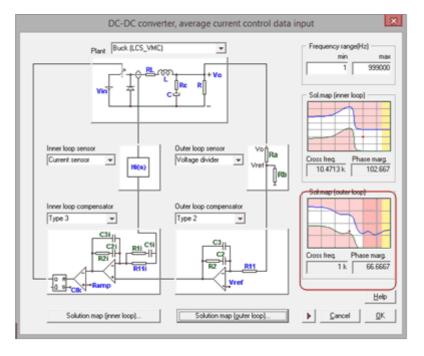

Once all the inner loop transfer functions have been defined, The cross frequency and the phase margin must be selected. Under the name of <u>Solution Map</u>, SmartCtrl provides the stable solution space in which all the possible combinations of cut off frequency and phase margin that lead to stable solutions are shown graphically. Just clicking on the "Solutions map (inner loop)" button the solution map corresponding to the inner loop is displayed.

The designer is asked to select the crossover frequency and the phase margin just by clicking within the white zone to continue.

This option is only available for pre-defined compensators.

Once the cross frequency and the phase margin have been selected, the solution map will be shown on the right of the side of the DC-DC average current control input data window. If, at any time, the two aforementioned parameters need to be changed, just click on the shown solution map. (See below figure)

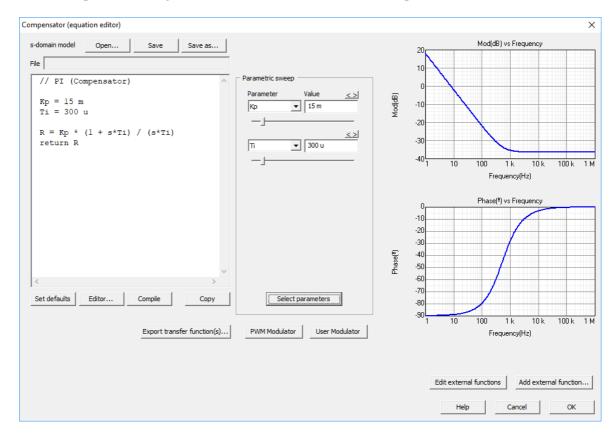

In case the user select the option **Equation Editor** for the inner loop compensator this window allows to open an existing one or to define with the editor the compensator transfer function.

In this case the Solutions Map is not available because the user is defining the regulator parameters, once the design is complete these parameters can be easily modified to check the solution stability in the graphic panels.

Now, the outer loop can be defined. First, the voltage sensor must be selected.

The different sensors available are the following:

- Voltage Divider

- •Embedded Voltage Divider

- Equation Editor (User Defined Sensor)

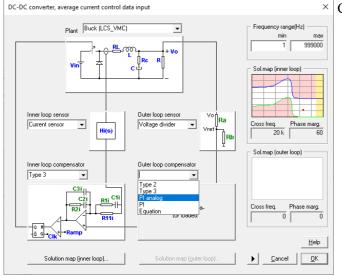

Next, the outer loop compensator must be selected.

Compensator types:

- <u>Type 3</u>

- Type 3 Unattenuated

- <u>Type 2</u>

- •Type 2 unattenuated

- •PI analog

- •PI

- •PI unattenuated

- •Single Pole

- •Single Pole unattenuated

- •Customer defined compensator using **Equation Editor**

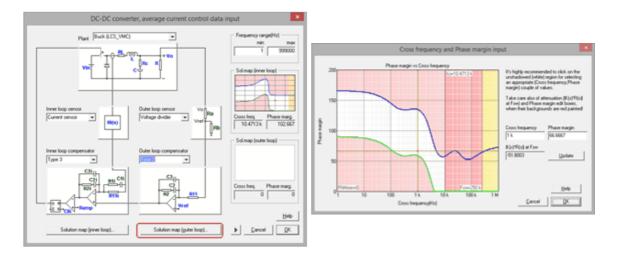

As well as in the case of the inner loop, the cross frequency and the phase margin must be selected. Also in this case, the <u>solution map</u> is available to help the selection of an stable solution. Press the "Solution map (outer loop)" button and the solution map will be displayed. Then select a point just by clicking within the white area.

It should be remarked that, due to stability constraints, the crossover frequency of the outer loop cannot be greater than the crossover frequency of the inner loop. In order to prevent the selection of an outer loop fc greater than the inner loop one, a pink shadowed area has been included in the solutions map of the outer loop.

Once the crossover frequency and the phase margin have been selected, the solution map will be shown on the right of the side of the DC-DC average current control input data window. If, at any time, the two aforementioned parameters need to be changed, just click on the shown solution map. (See next figure)

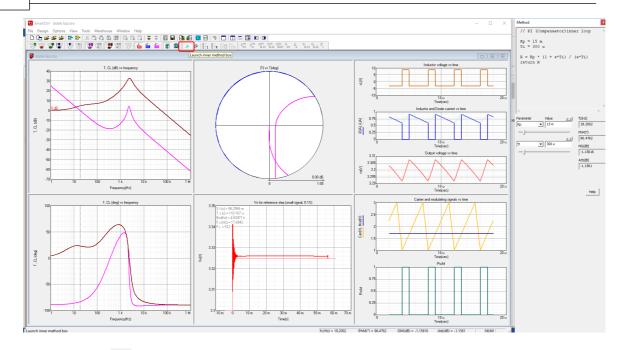

Now accept the selected configuration and confirm the design, the program will automatically show the performance of the system in terms of frequency response, transient response... (See <u>Graphic and text panels window</u> for detailed information)

In case the user selected for both loops the customized compensator using the Equation Editor, once accepted the design, the compensator parameters sweep in the Method box allows the user to check the design stability.

Using the icon "Launch inner method box" in the toolbar, the user can modify the inner loop compensator parameters.

Using the icon (\*\*Launch outer method box" in the toolbar, the user can modify the outer loop compensator parameters.

## 1.4.5 Power factor corrector

Navigation: SmartCtrl > Design a predefined topology >

#### Power factor corrector

Previous Top Next

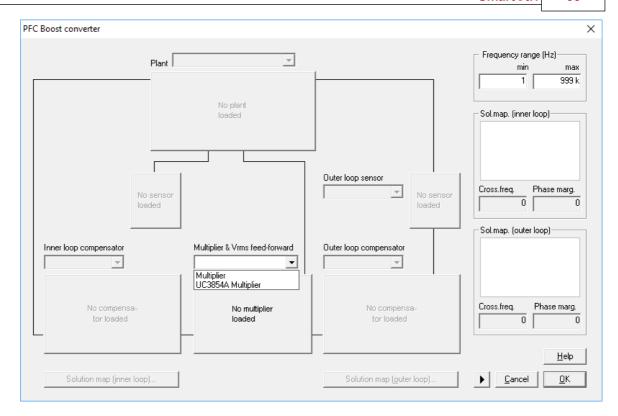

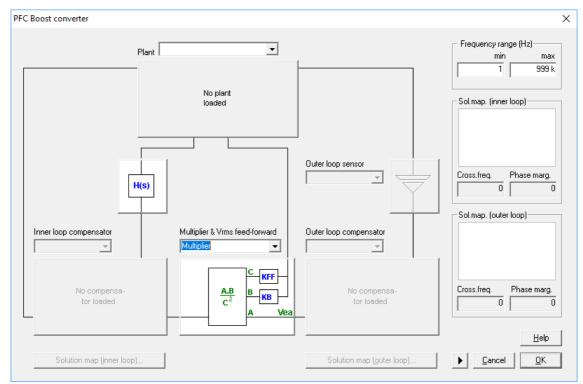

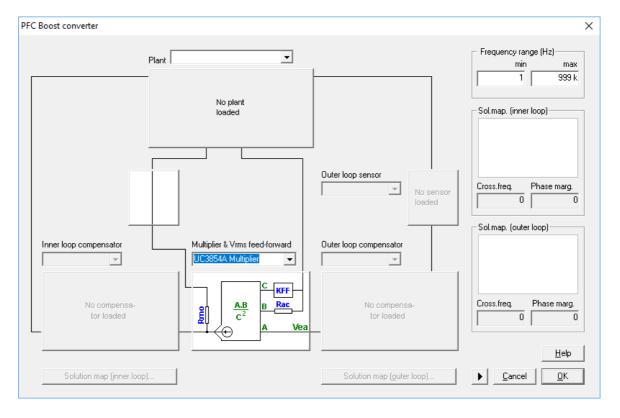

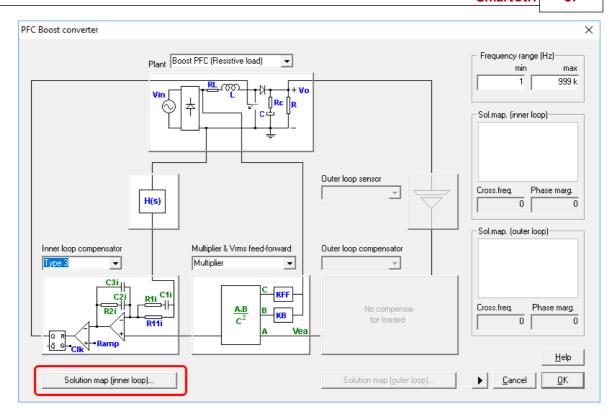

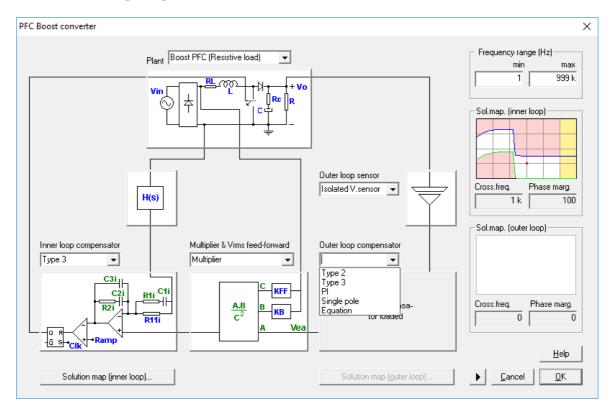

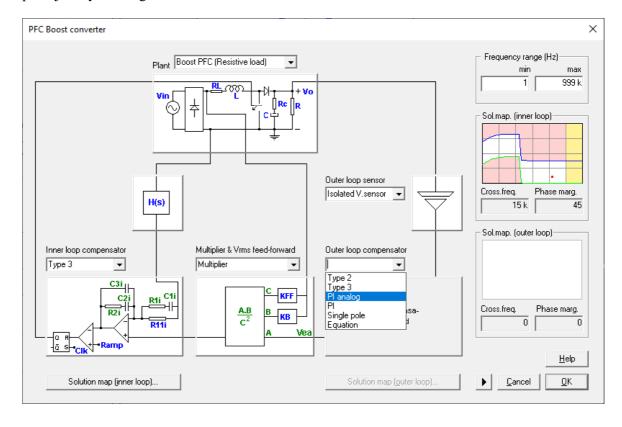

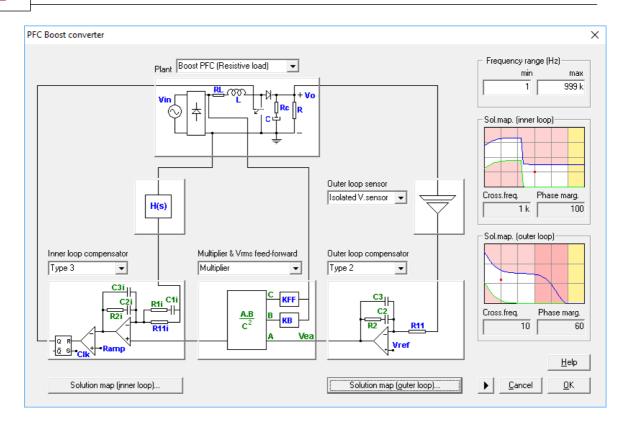

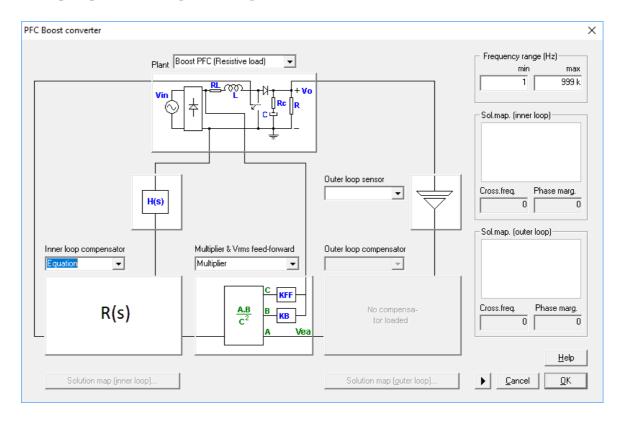

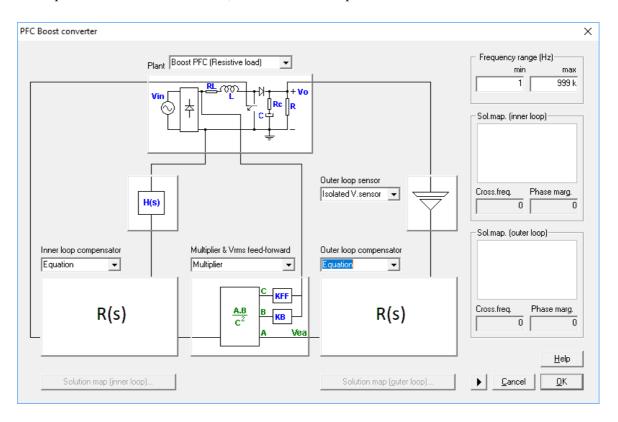

The power factor corrector based on a boost topology has a double control loop, formed by an inner (inductance) current loop and an outer voltage mode loop. The double loop setup must be built sequentially. The program will guide you to build it, enabling the following step and keeping everything else disabled.

The first step chooses between the two types of multiplier and Vrms feed-forward:

- •Multiplier: A generic, parametrizable multiplier, with a Hall Effect current sensor.

- •<u>UC3854A Multiplier</u>: UC3854A Multiplier: An UC3854A commercial multiplier, with its external resistors to be chosen.

Depending on the first choice, there are two different options to generate the power factor corrector.

If a Generic Multiplier is selected, the current is sensed by the Hall Effect sensor H(s).

Otherwise, if the selection is UC3854A multiplier, the current sensor is implemented by means of the resistor Rs.

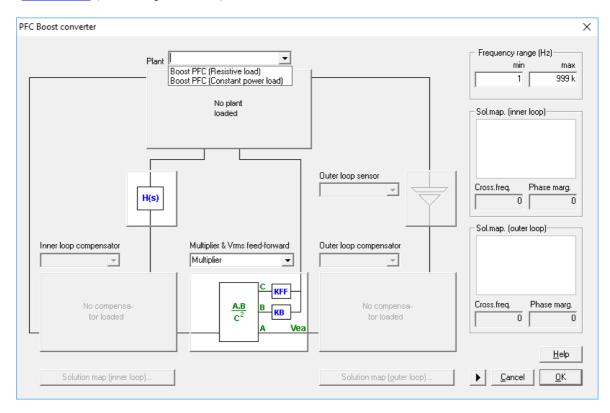

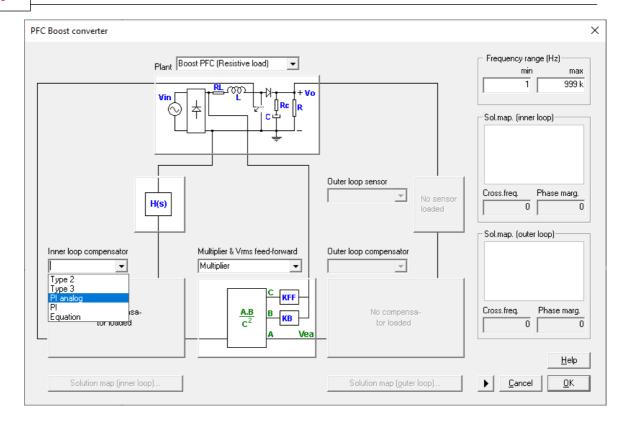

Next, the plant must be selected. The predefined plants are the following:

- •Boost PFC (Resistive load)

- •Boost PFC (Constant power load)

Next, the inner control loop will be configured: since the current sensor has been already set, it is necessary to select the inner loop compensator.

#### Compensator types:

- Type 3 (It is only available for Multiplier option)

- •**Type 2**

- •<u>PI</u>

- •PI analog

- •User defined compensator: Equation Editor

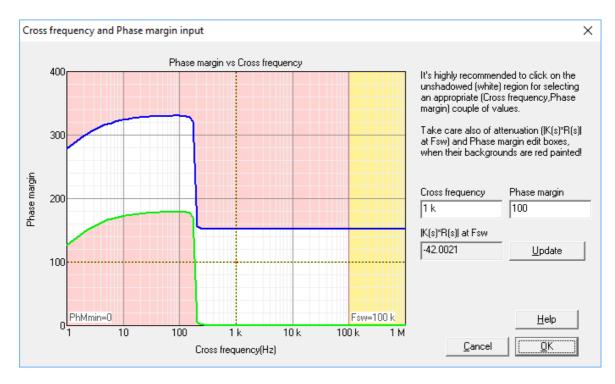

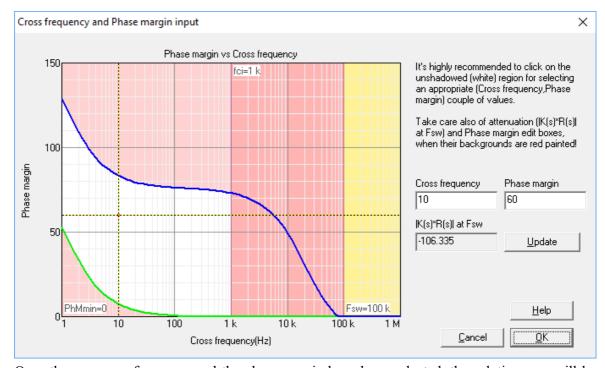

Once all the **inner loop** transfer functions have been defined, the crossover frequency and the phase margin must be selected. Under the name of <u>Solution Map</u> (only for predefined compensators), SmartCtrl provides the stable solution space in which all the possible combinations of crossover frequency and phase margin that lead to stable solutions are shown graphically. Just clicking on the "Solutions map (inner loop)" button the solution map corresponding to the inner loop is displayed.

The designer is asked to select the crossover frequency and the phase margin just by clicking within the white zone to continue.

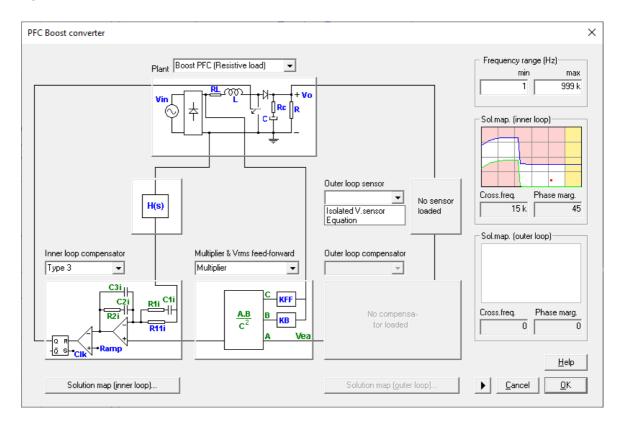

Once the crossover frequency and the phase margin have been selected, the solution map will be shown on the right side of the PFC Boost converter input data window. If, at any time, the two aforementioned parameters need to be changed, just click on the inner loop solution map. (See next figure).

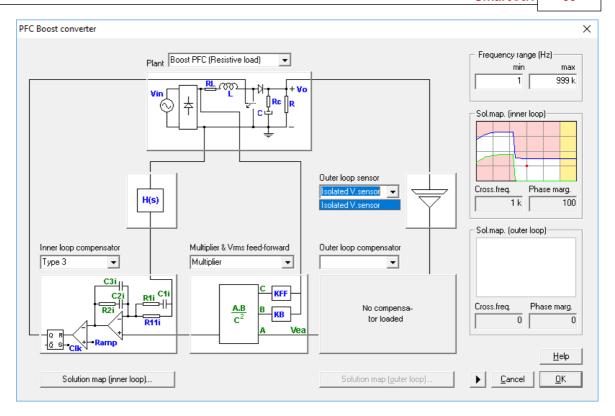

Now, the **outer loop** can be defined. First, the voltage sensor must be selected.

The voltage sensors available are the following:

#### For Multiplier option:

- •Isolated V sensor

- Equation Editor (User Defined Sensor)

#### For UC3854A Multiplier option:

- Voltage Divider

- Embedded Voltage Divider

- **•**Equation Editor (User Defined Sensor)

Next, the outer loop compensator must be selected.

Outer Loop compensator types depending on the sensor previously selected:

| For multiplier option:                                                                                                                     | For UC3854 multiplier option:                                                                                              |                                                                                                                                                |                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                            | For Voltage<br>Divider sensor:                                                                                             | For Embedded<br>Voltage Divider<br>sensor:                                                                                                     | For user defined sensor (Equation Editor):                                                                                                 |

| <ul> <li>Type 3</li> <li>Type 2</li> <li>PI</li> <li>PI analog</li> <li>Single Pole</li> <li>User defined using Equation Editor</li> </ul> | <ul> <li>Type 2</li> <li>PI</li> <li>PI analog</li> <li>Single Pole</li> <li>User defined using Equation Editor</li> </ul> | <ul> <li>Type 2 unattenuated</li> <li>PI unattenuated</li> <li>Single Pole unattenuated</li> <li>User defined using Equation Editor</li> </ul> | <ul> <li>Type 2</li> <li>Type 3</li> <li>PI</li> <li>PI analog</li> <li>Single Pole</li> <li>User defined using Equation Editor</li> </ul> |

As well as in the case of the inner loop, the cross frequency and the phase margin must be selected. Also in this case, the <u>solution map</u> (only for predefined compensators) is available to help the selection of a stable solution.

Press the "Solution map (outer loop)" button and the solution map will be displayed. Then select a point just by clicking within the white area.

It should be remarked that, due to stability constraints, the crossover frequency of the outer loop cannot be greater than the crossover frequency of the inner loop. In order to prevent the selection of an outer loop fc greater than the inner loop one, a pink shadowed area has been included in the solutions map of the outer loop.

Once the crossover frequency and the phase margin have been selected, the solution map will be shown on the right side of the DC-DC average current control input data window. If, at any time, the two aforementioned parameters need to be changed, just click on the outer loop solution map. (See next figure)

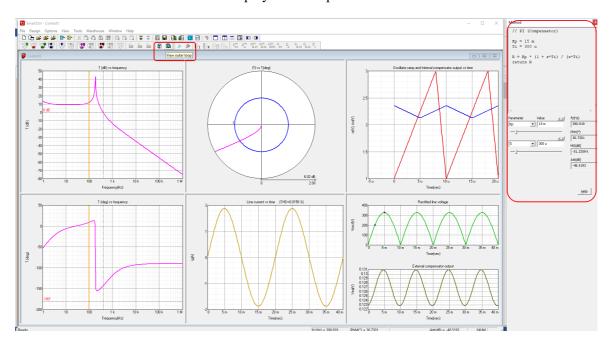

Once everything is set, accept the selected configuration and confirm the design, the program will automatically show the performance of the system in terms of frequency response, line current shape... (See <u>Graphic panel window</u> for detailed information).

Once the design has been generated, two possible warning messages can appear in the solution map window:

- · In the case of a single pole compensator in the outer loop, which is a typical compensator for power factor correctors, the gain at low frequency may be low. A warning appears when the estimated Vo (shown in the method panel) differs from the specified one in more than 10%. In these cases, a compensator with a higher gain at low frequency is recommended.

- · The line current waveform is calculated assuming that the current loop follows perfectly well the reference generated by the outer loop. However, in some occasions there is a zero-cross distortion and the actual line current would differ from the one represented. In these cases, a warning message appears. The cross-frequency of the inner loop compensator should be increased to minimize this problem.

In the method panel, additional information is provided both for the inner loop and the outer loop:

•Attenuation (fsw)(dB). This is the attenuation in dB achieved by the combination of the sensor and the compensator at the switching frequency. Since the reference for the inner loop is generated by the outer one, it must be enough to avoid making the system unstable.

- •Attenuation (2fl)(dB). This is the attenuation in dB achieved by the combination of the sensor and the compensator at twice the line frequency (100 Hz or 120 Hz). Since the reference for the inner loop is generated by the outer one, it must be enough to avoid making the system unstable.

- •Estimated Vo (V). This is the estimated output voltage of the converter. This parameter is important because, if the frequency gain of the open loop transfer function is not high enough, there will be a steady-state error and the estimated output voltage can be different from the specified output voltage. As mentioned above, if the estimated Vo (shown in the method panel) differs from the specified one in more than 10%, a warning will be displayed.

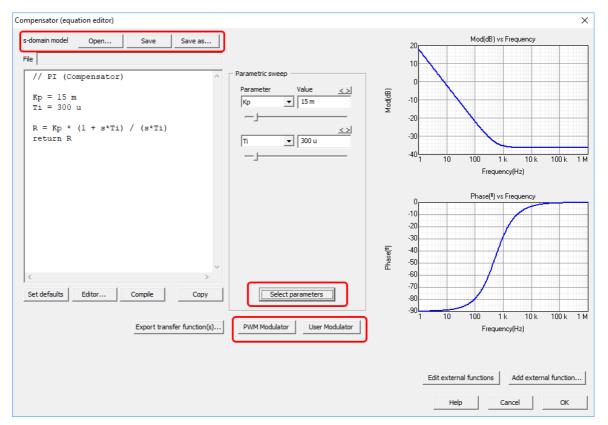

In case the user selects a **customer defined compensator** using the Equation Editor, just follow the steps explained in <u>Compensator</u> (Equation Editor)

This option can be selected for both, inner and outer loops.

For customer defined compensator the solutions map will not be available; use the buttons in the view toolbar to change the graphic view between inner and outer loop and to adjust the inner and outer loop compensator values in the method Box.

View inner loop

View outer loop

Launch inner method box / Display inner loop results

Enables or disables the display of the compensator calculation method toolbox. Launch outer method box or Method box / Display outer loop results

Finally, the flowchart to generate the types of the power factor is the following:

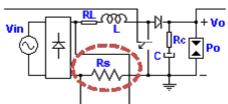

#### 1.4.5.1 Power stage

(- 4 -)

Navigation: SmartCtrl > Design a predefined topology > Power factor corrector >

## **Boost PFC power stage**

Previous Top Next

The Boost PFC is based on a double loop control scheme, and therefore the output voltage and the current through the inductor are sensed simultaneously. There are Four options for the plant, depending on the load and the multiplier:

<u>Generic multiplier</u> + <u>Boost PFC</u> (Resistive load)

**Generic multiplier + Boost PFC**

<u>UC3854A multiplier</u> + <u>Boost PFC</u> (Resistive load)

<u>UC3854A multiplier</u> + <u>Boost PFC</u> (<u>Constant power load</u>)

The current loop is designed considering a piecewise linear model of the plant: using quasi-static assumption, the small signal model for each operating point is calculated as in a DC/DC boost converter.

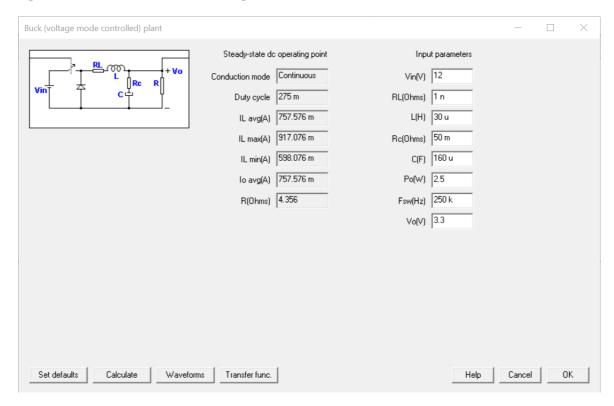

The input data variables are listed and defined below:

## Input data

| V <sub>in</sub> (rms  | Input Voltage (V)                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| )                     |                                                                                                                                                                                                                                                                                                                                                                                                                |

| $R_L$                 | Equivalent Series Resistor of the Inductance (Ohms)                                                                                                                                                                                                                                                                                                                                                            |

| L                     | Inductance (H)                                                                                                                                                                                                                                                                                                                                                                                                 |

| Rc                    | Equivalent Series Resistor of the output capacitor (Ohms)                                                                                                                                                                                                                                                                                                                                                      |

| C                     | Output Capacitor (F)                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>o</sub>        | Output Voltage (V)                                                                                                                                                                                                                                                                                                                                                                                             |

| R                     | Load Resistor (Ohms)                                                                                                                                                                                                                                                                                                                                                                                           |

| P <sub>o</sub>        | Output Power (W)                                                                                                                                                                                                                                                                                                                                                                                               |

| wta                   | Line angle(°). The current loop is designed considering the plant calculated for this operating point. This line angle is indicated as a red dot in the output panel that represents the <a href="Rectified voltage and external compensator">Rectified voltage and external compensator</a> output (See <a href="Graphic and text panels window">Graphic and text panels window</a> for detailed information) |

| F <sub>SW</sub>       | Switching frequency (Hz)                                                                                                                                                                                                                                                                                                                                                                                       |

| Line<br>freque<br>ncy | Line frequency (Hz)                                                                                                                                                                                                                                                                                                                                                                                            |

#### 1.4.5.2 Graphic panels

Navigation: SmartCtrl > Design a predefined topology > Power factor corrector >

## Graphic panels

Previous Top Next

The window is divided in six different panels:

The graphic panels are:

**Bode plot Module (dB)**

Bode plot Phase (°)

Nyquist diagram

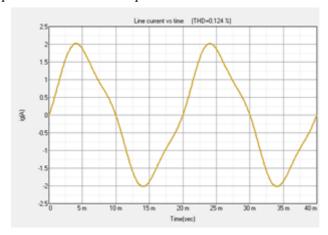

Line current

Oscillator ramp and internal compensator

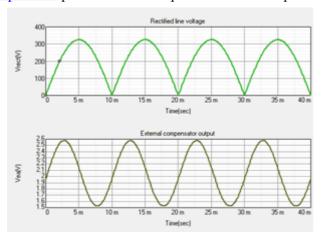

Rectified voltage and external compensator output

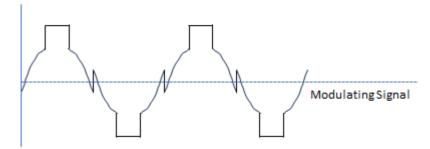

#### Oscillator ramp and internal compensator

Navigation: SmartCtrl > Design a predefined topology > Power factor corrector > Graphic panels

# Oscillator ramp and internal compensator

Previous Top Next

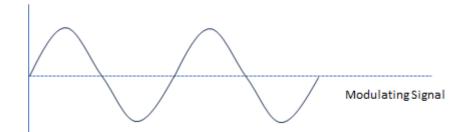

This graphic panel provides information about the output of the inner control compensator (blue line) compared to the oscillator ramp (red line). The output of the internal compensator is represented for the line angle corresponding to the maximum current ripple through the inductor. This line angle is identified by means of a blue dot in the <a href="Rectified voltage and external compensator output">Rectified voltage and external compensator output</a> graphical panel.

This comparison can be useful to determine whether there could be oscillations. If the slopes of both functions are too similar, there could be more than one intersection per period.

#### Line current

Navigation: SmartCtrl > Design a predefined topology > Power factor corrector > Graphic panels

Line current

Previous Top Next

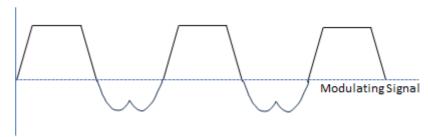

This graphic panel provides information about the line current and its harmonic distortion. The line current waveform is calculated assuming that the current loop follows perfectly the reference generated by the outer loop. However, in some occasions there is a zero-cross distortion and the actual line current would differ from the one represented. In these cases, a warning message would appear in the solution map window.

#### Rectified voltage and external compensator output

Navigation: SmartCtrl > Design a predefined topology > Power factor corrector > Graphic panels

# Rectified voltage and external compensator output

Previous Top Next

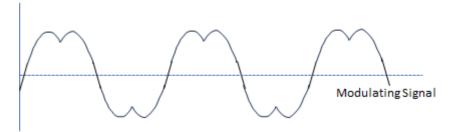

This graphic panel provides information about the external compensator output voltage. Its phase shift compared to the rectified voltage can be assessed. If the compensator output voltage has not an appropriate phase shift compared to the rectified voltage (reference), the line current distortionwill increase.

The current loop is designed considering a piecewise linear model of the plant. The current plant represented in the Bode plot panels (see <u>Graphic panels window</u>) corresponds to the operating point marked with a red dot in the rectified voltage. The small signal model for the plant is calculated as in a DC/DC boost converter for this operating point. This dot can be moved by clicking and dragging with the mouse, resulting in a variation of the operating point. As the dot changes its position, the Bode plot corresponding to the inner loop varies, as well as the attenuation information in the K-factor panel refreshes according to the indicated operating point.

The blue dot in the rectified voltage represents the operating point that corresponds to the maximum current ripple through the inductor. The gr aphics in the <u>Oscillator ramp and internal compensator</u> panel have been represented for this operating point.

## 1.4.5.3 Multipliers

### Multiplier

Navigation: SmartCtrl > <u>Design a predefined topology</u> > <u>Power factor corrector</u> > Multipliers >

## Multiplier

Previous Top Next

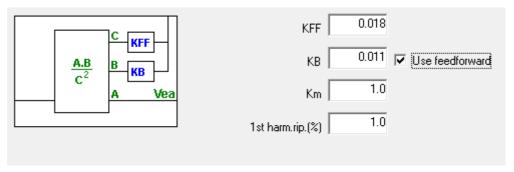

Using feedforward:

The **multiplier** has the following parameters:

**KB** Gain of the current reference for the inner loop.

Km Multiplier gain.

And, when the use of feed-forward is selected:

**KFF** Gain of the feed-forward. It is the ration between the rms input voltage and the average input voltage to the multiplier.

**1st harm.rip.(%)** Ratio between the amplitude of the first harmonic of the rectified input voltage and its average value.

### UC3854A multiplier

Navigation: SmartCtrl > <u>Design a predefined topology</u> > <u>Power factor corrector</u> > Multipliers >

## UC3854A multiplier

Previous Top Next

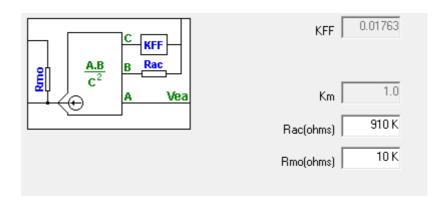

The UC3854A multiplier has the following parameters:

**KFF** Gain of the feed-forward. It is the ration between the rms input voltage and the average input voltage to the multiplier.

Km Multiplier gain.

Rac Resistance to introduce the current reference for the inner loop (Ohms)

Rm Resistance to convert the multiplier output current into a voltage reference for the inner

o compensator (Ohms)

# 1.5 Desing a generic topology

Navigation: SmartCtrl >

C-1-

## Design a generic topology

Previous Top Next

SmartCtrl not only helps the designer when a pre-defined power converter is considered, it also allows the design of the control loop of any generic converter.

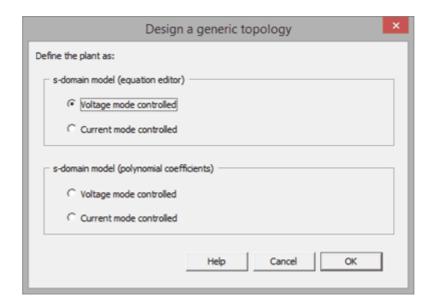

To carry out the design of the control when the plant is not a pre-defined DC-DC converter, the plan must be provided either by means of an s-domain transfer function or importing the plant frequency response from a .txt file. Depending of the desired input method, the designer must select between:

- s-domain model editor

- Import frequency response data from a .txt file

# 1.5.1 s-domain model editor

Navigation: SmartCtrl > Desing a generic topology >

# s-domain model editor

Previous Top Next

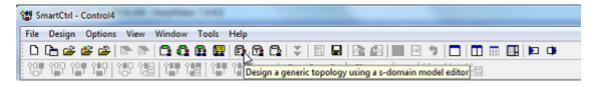

The s-domain model editor is available at:

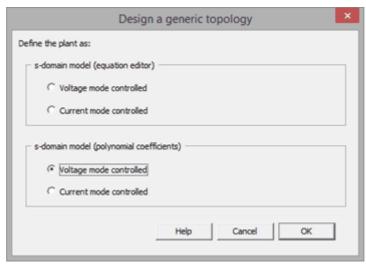

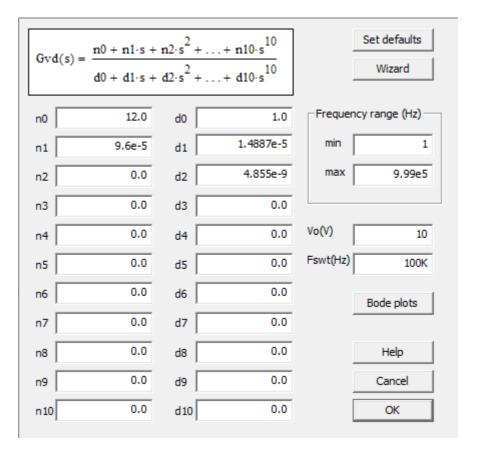

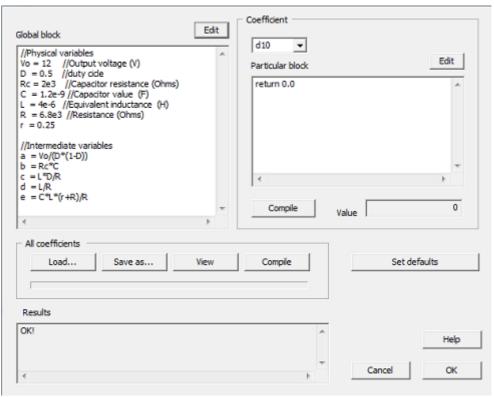

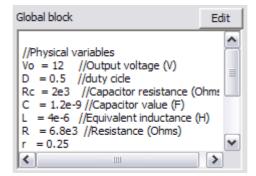

The s-domain model editor provides two different options in order to define the s-domain transfer function plant:

- •s-domain model (equation editor)

- •s-domain model (polynomial coefficients)

In both cases, the user must select the control strategy.

#### 1.5.1.1 Import frequency response data from .txt file

Navigation: SmartCtrl > Desing a generic topology > s-domain model editor >

# Import frequency response data from .txt file

Previous Top Next

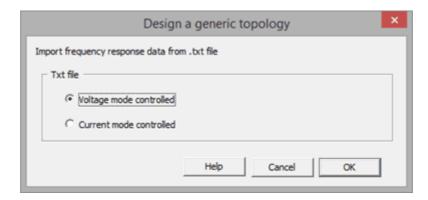

The "Import frequency response form a .txt file" is also available at:

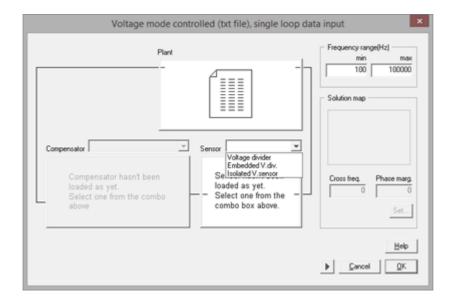

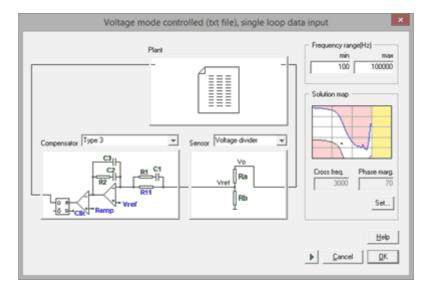

SmartCtrl allows the designer to import his own transfer plant function and design an appropriate control loop. This feature is only available for single loop designs. To define the imported transfer function the user must specify the intended control type:

Take into account that, whether the imported plant is current mode controlled or voltage mode controlled, the single loop design process will be the same. The only difference is related to the available sensors, which are different for each case.

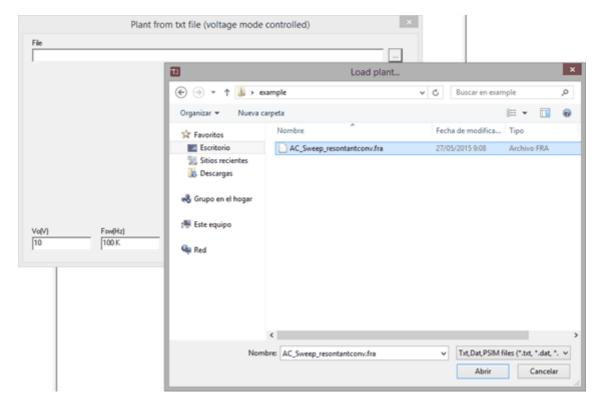

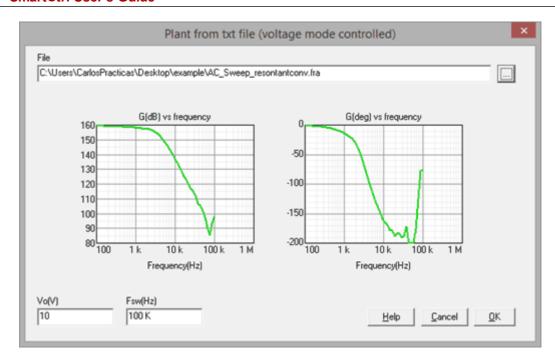

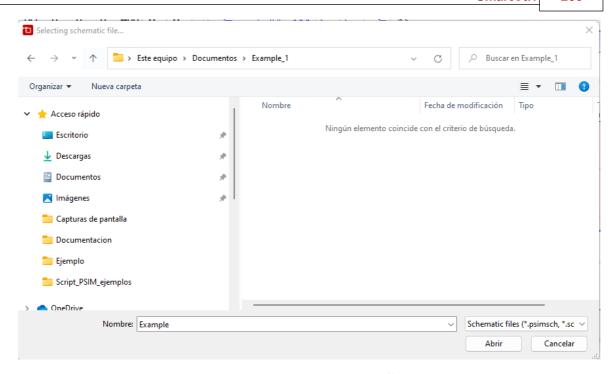

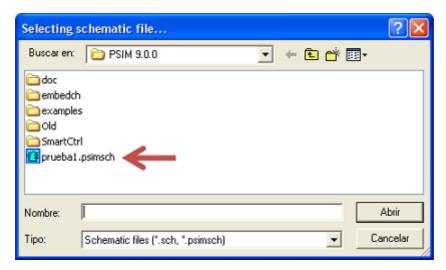

Once the control type has been selected, the file that contains the plant frequency response must be selected. SmarCtrl is able to load the following file formats: \*.dat, \*.txt, \*.fra

Once the file has been selected, the data is loaded to SmartCtrl and the magnitude and phase are displayed as depicted in the next figure.

And some additional data such as the output voltage (only in voltage mode control) and the switching frequency must be specified.

Click OK to continue.

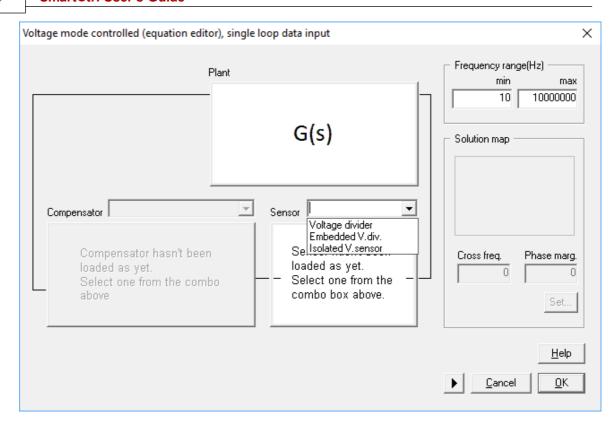

Depending upon it is a current mode controlled or voltage mode controlled, the available sensors are the following:

Voltage mode controlled

- Voltage divider

- Embedded Voltage

Divider

- Isolated V. sensor

Current mode controlled

- Current sensor

- Hall effect sensor

Finally, select the compensator.

Once the system has been defined, SmartCtrl calculates the <u>Solutions Map</u> (only for predefined compensators), in which it is shown graphically all the combinations of crossover frequency and phase margin that leads to stable solutions. To continue, click on set and the solutions map will be displayed. After that, select a point within the stable solutions area (white area) and then click OK.

Now confirm the design and the program will automatically show the performance of the system in terms of frequency response, transient response. (See <u>Graphic and text panels</u> window for detailed information)

In case the user has selected a customized compensator using the equation editor, use the compensator parameter sweep available in the Method box instead of the solutions map.

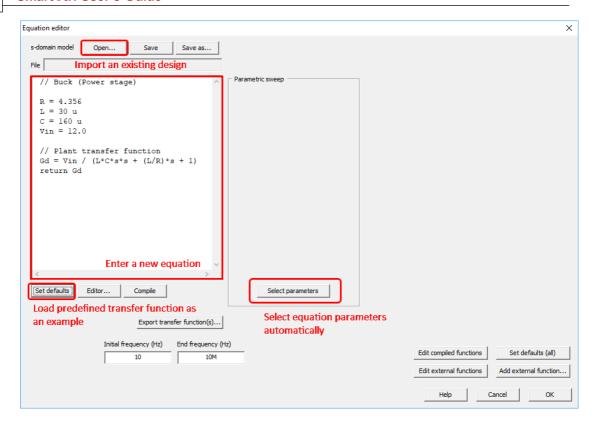

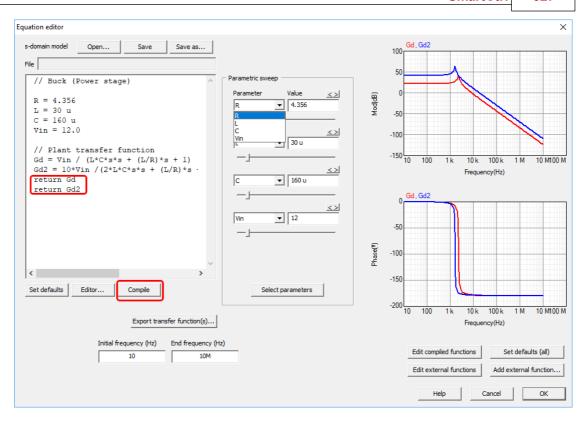

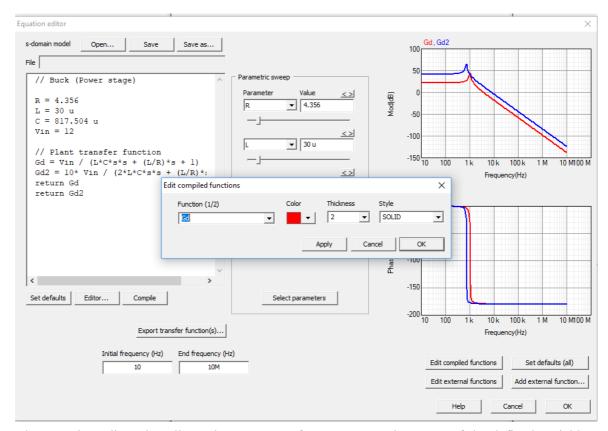

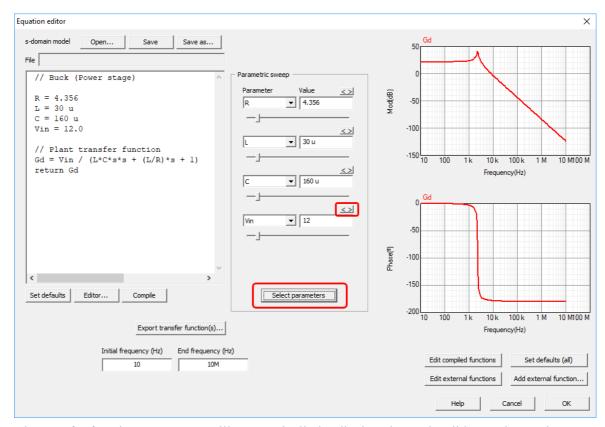

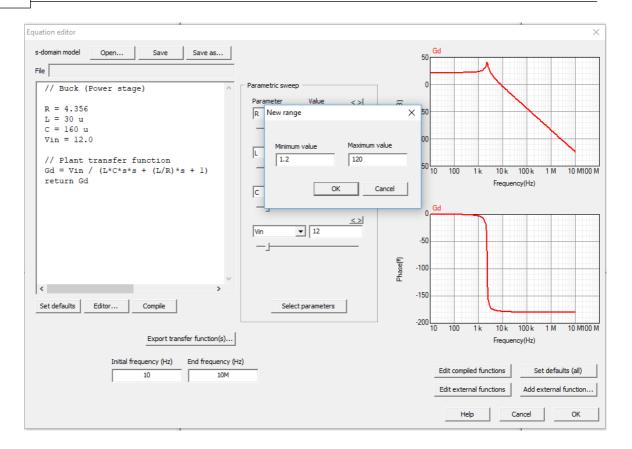

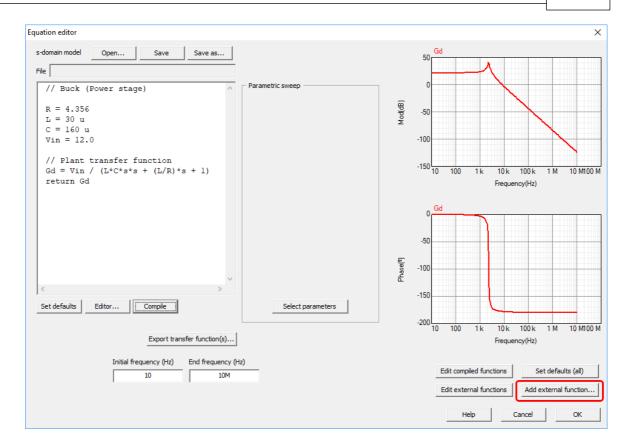

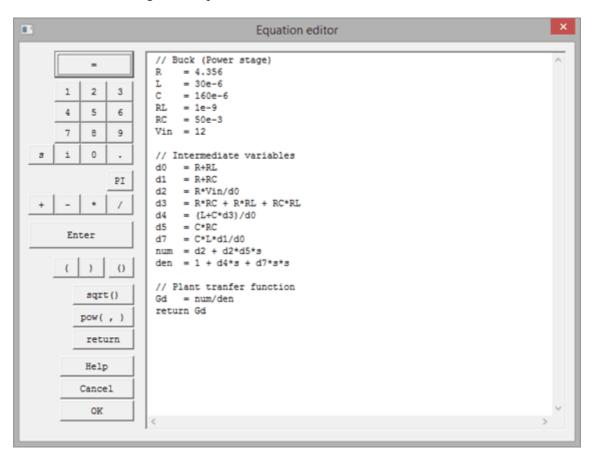

# 1.5.1.2 s-domain model (equation editor)

Navigation: SmartCtrl > Desing a generic topology > s-domain model editor >

# s-domain model (equation editor)

Previous Top Next

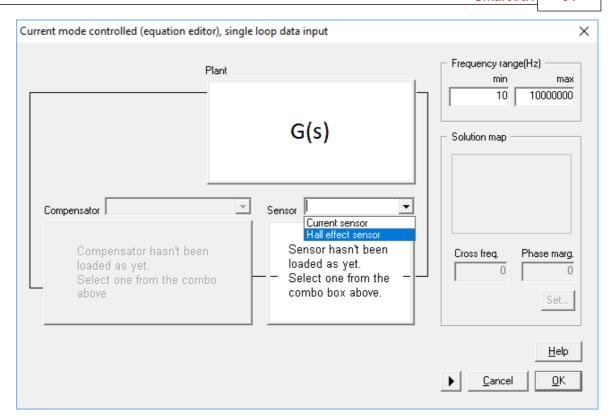

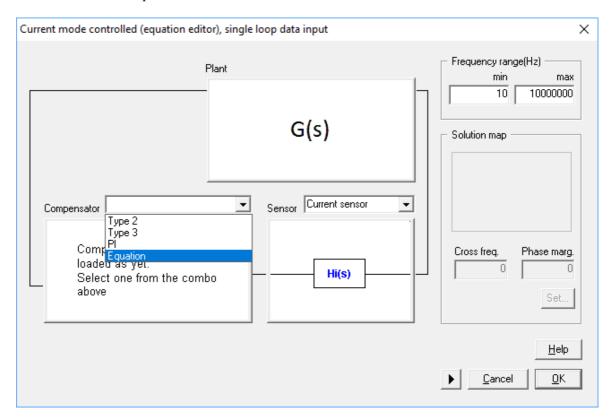

The s-domain model editor (equation editor) provides two different options depending on whether the defined plant transfer function is intended for:

- Voltage mode control (VMC)

- Current mode control (CMC)

F 7 =

# s-domain model (equation editor) VMC

Navigation: SmartCtrl > Desing a generic topology > s-domain model editor > s-domain model (equation editor) >

# s-domain model (equation editor) VMC

Previous Top Next

When the power converter is defined through its s-domain transfer function, the design procedure is as follow:

First, the user must define the s-domain transfer function of the plant, choosing amongst two different options:

- · Import a previous design (click on open)

- · Define a new transfer function (click on editor).

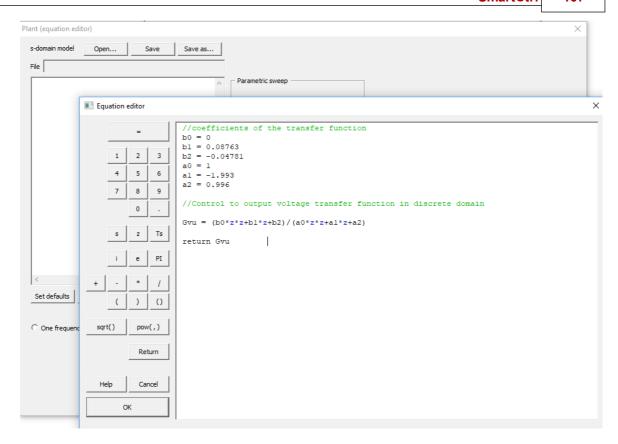

Once the equation has been introduced:

- · Click on "Save" to save the mathematical equations in a text file with extension .tromod

- · Click on "compile" to continue.

- · If desired, the frequency response of the transfer function can be exported as a .txt file by clicking on "Export transfer function".

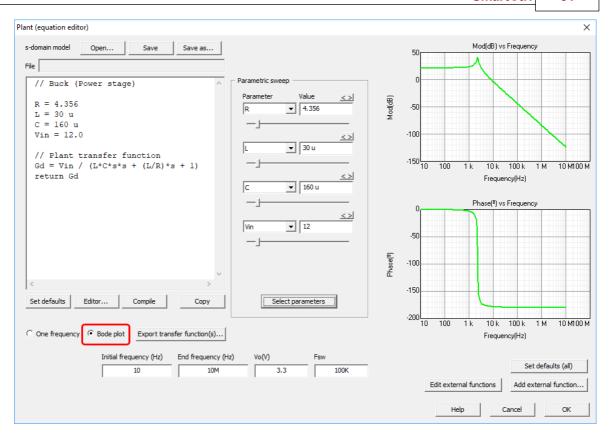

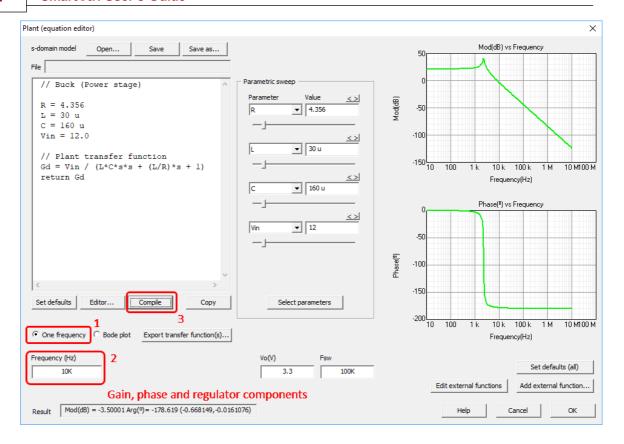

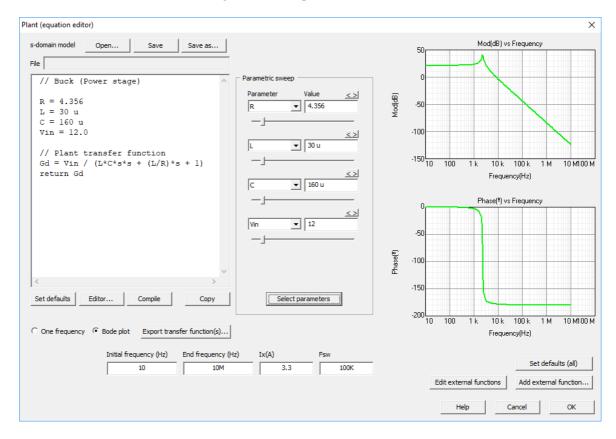

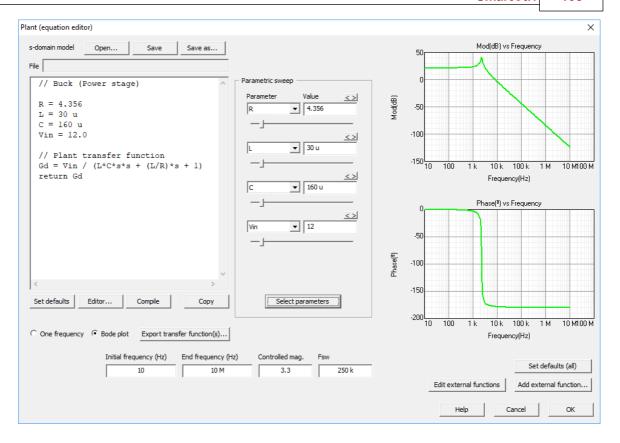

The option "Bode plot" is selected by default, the frequency response of the previously defined transfer function is shown on the right hand side panels.

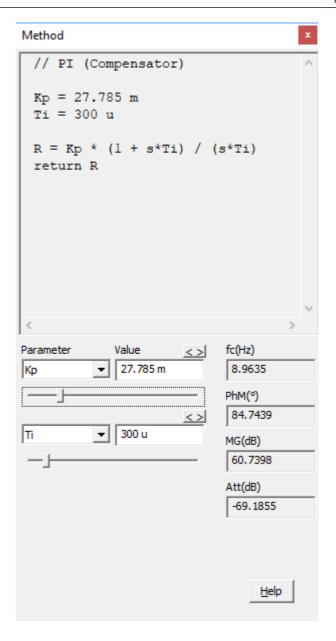

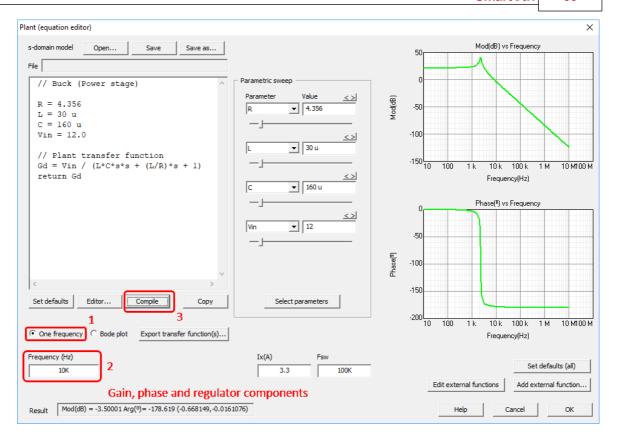

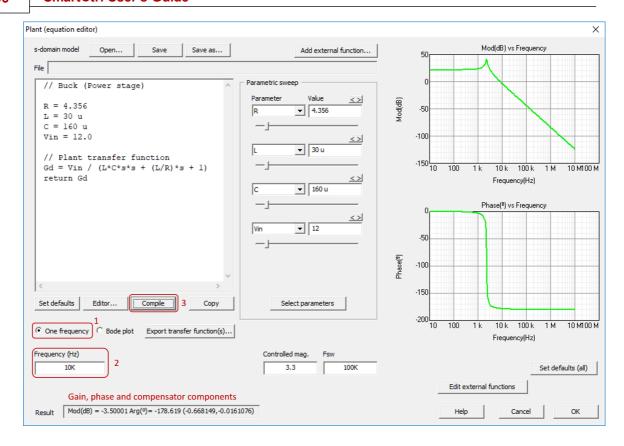

To check the gain, phase and rectangular components of the frequency response at a particular frequency, the option "One frequency" is provided.

As shown in the following figure: first select the option "one frequency", secondly specify the frequency and finally, click on compile and the gain, phase and rectangular components at the specified frequency are shown below.

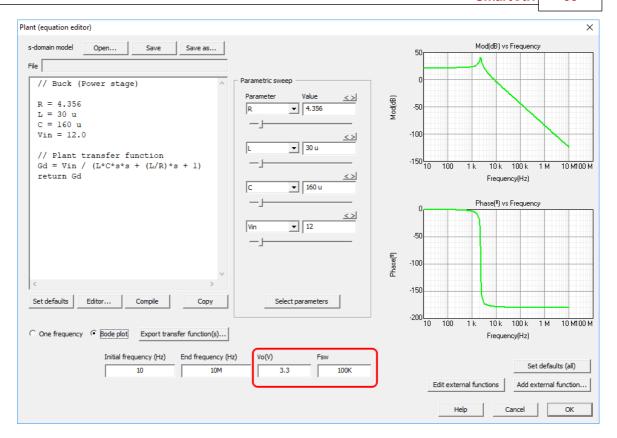

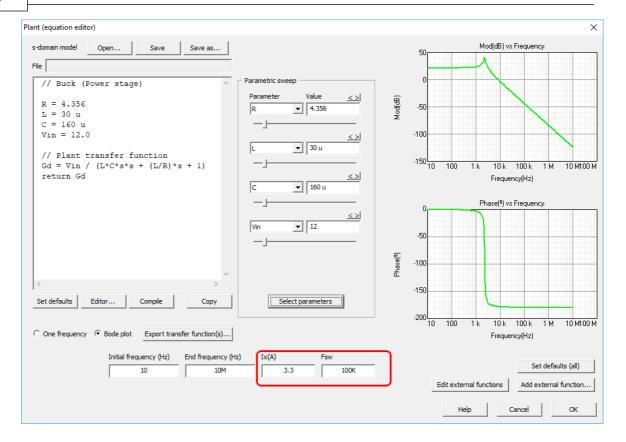

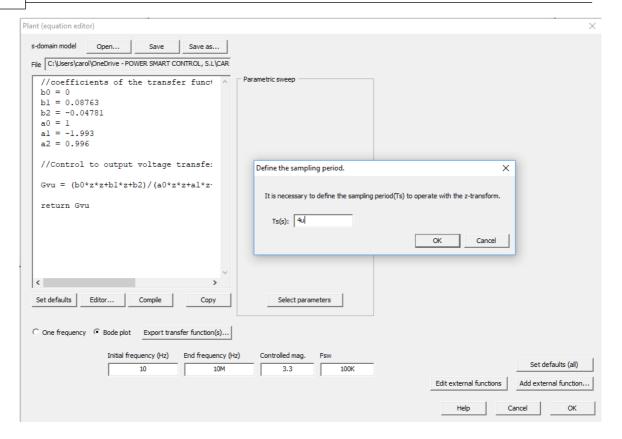

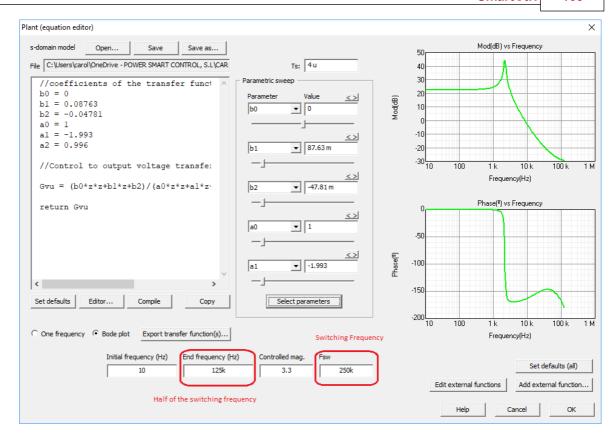

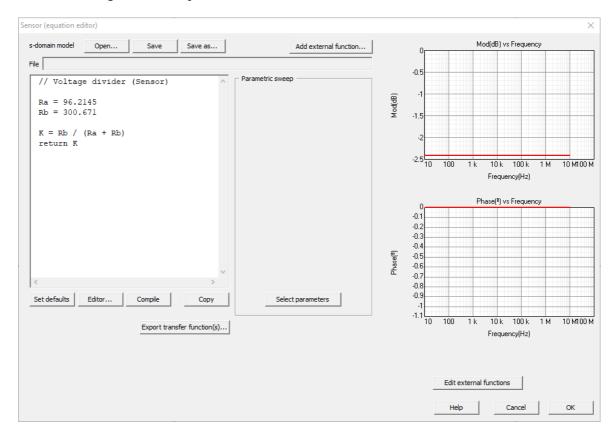

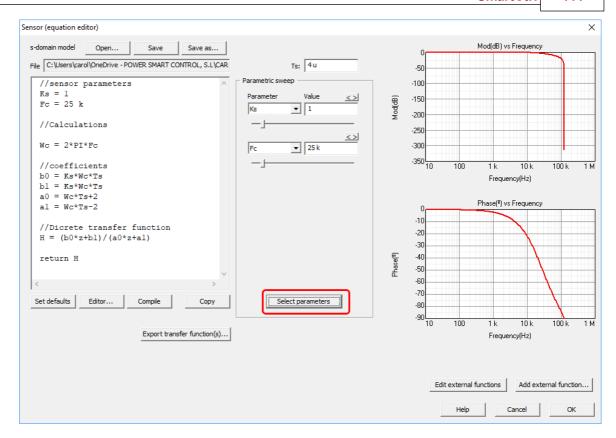

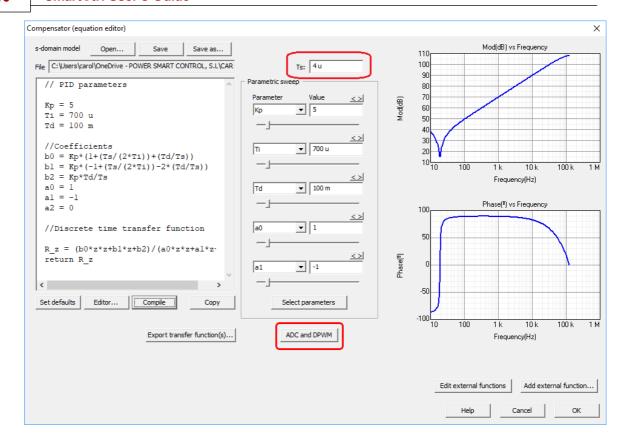

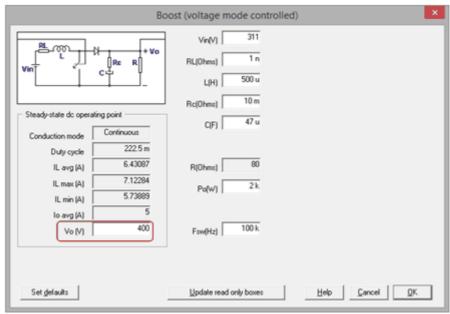

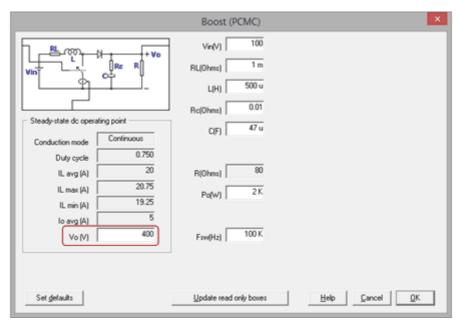

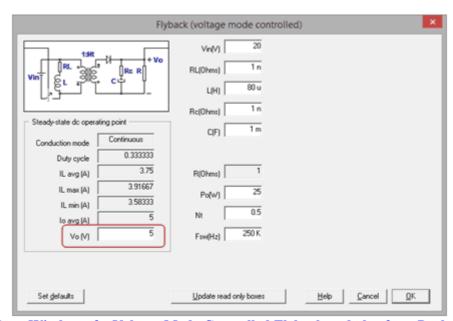

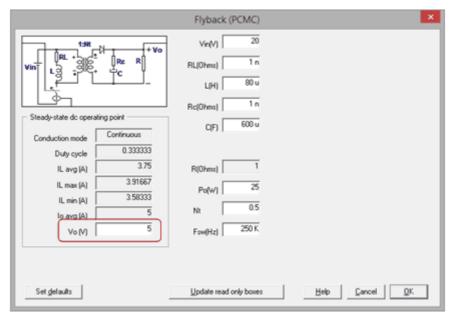

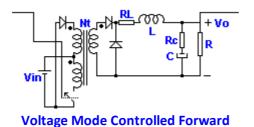

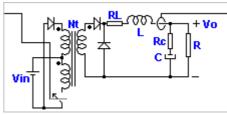

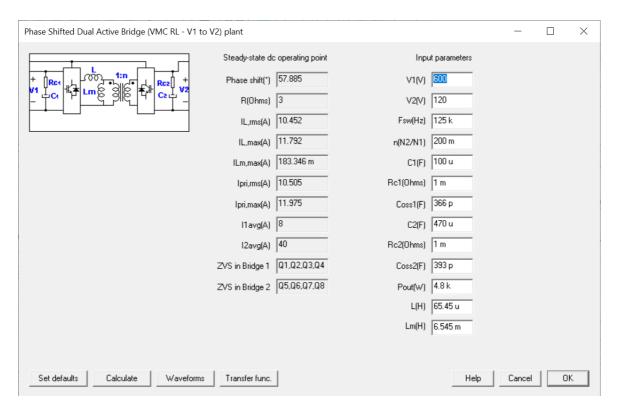

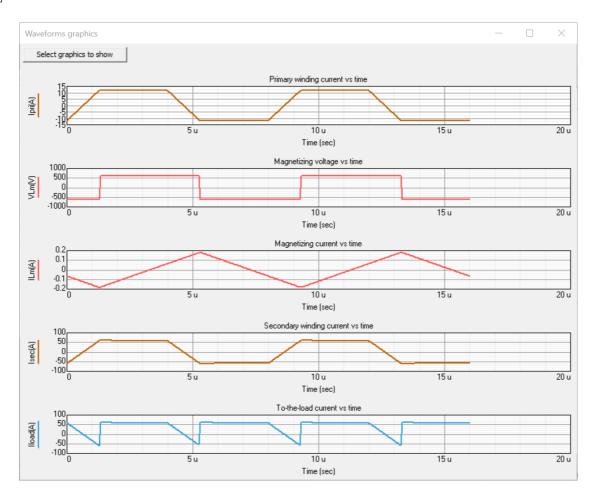

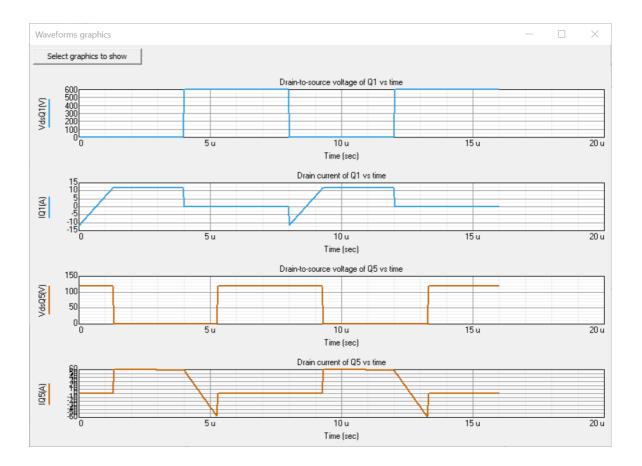

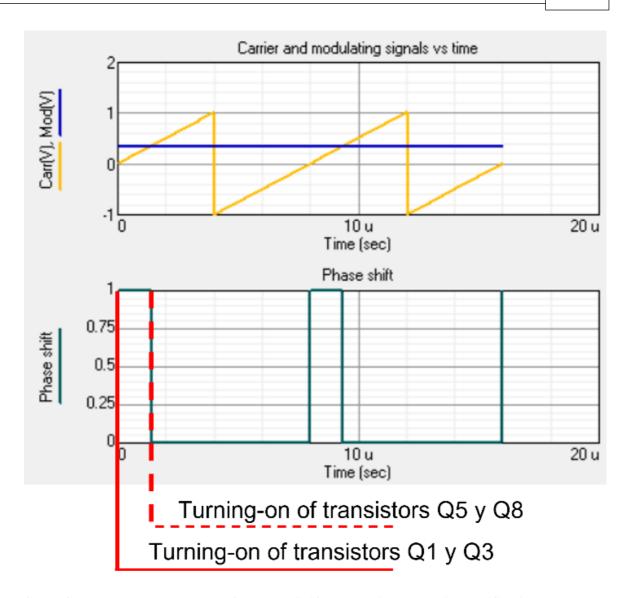

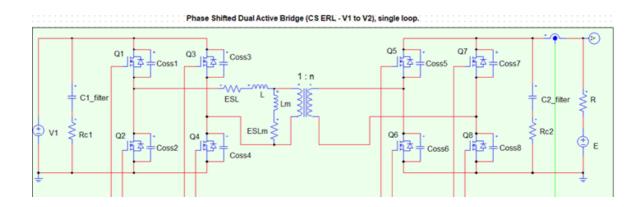

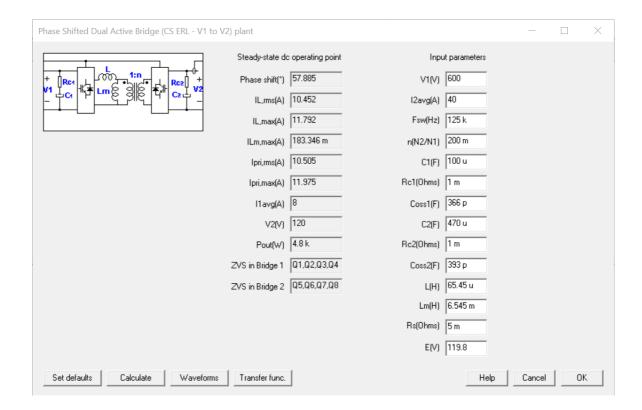

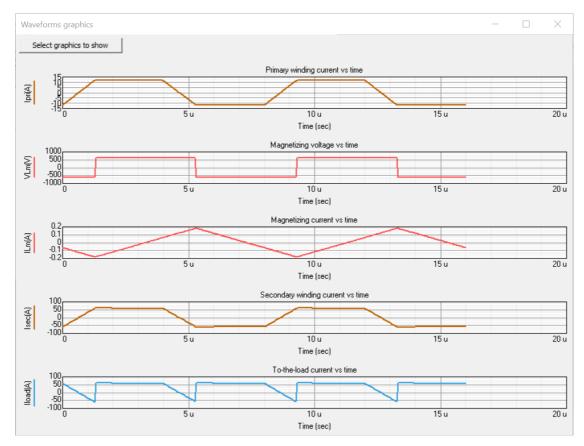

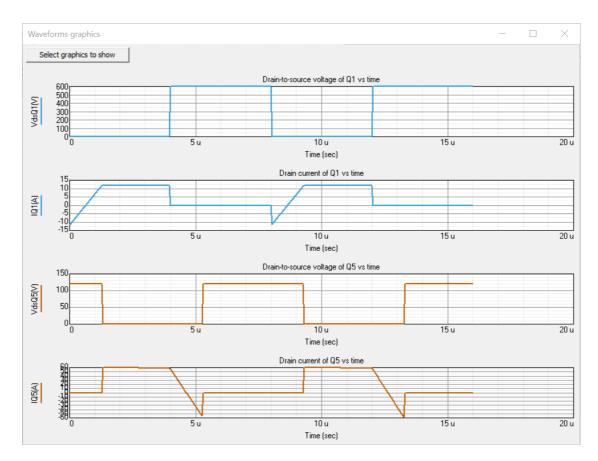

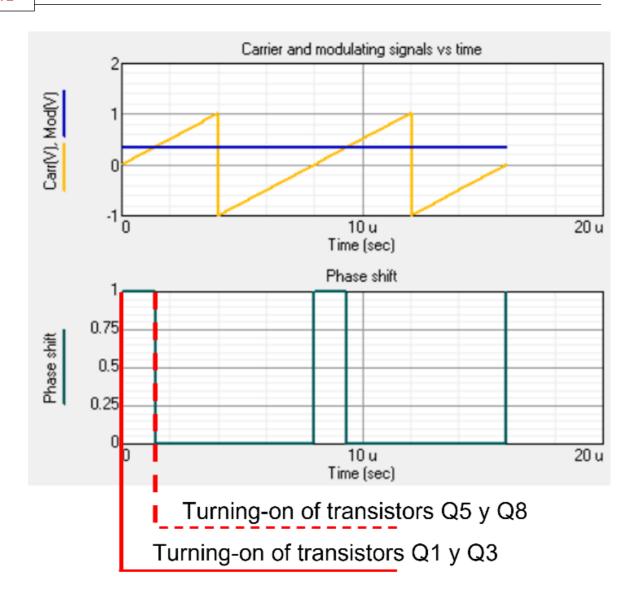

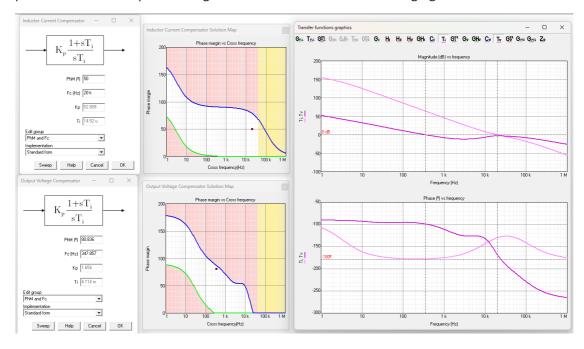

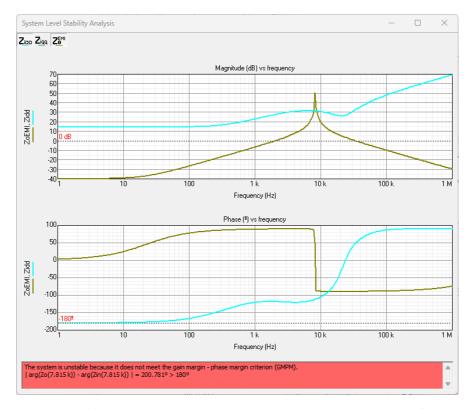

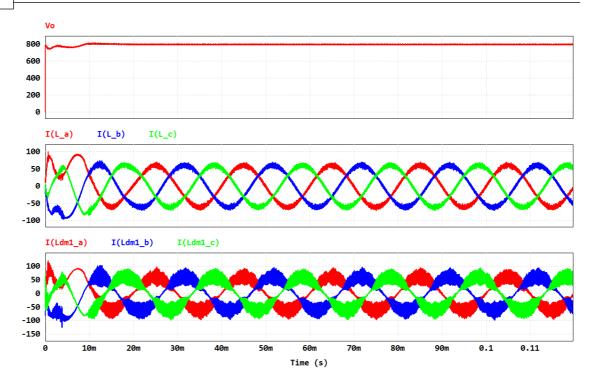

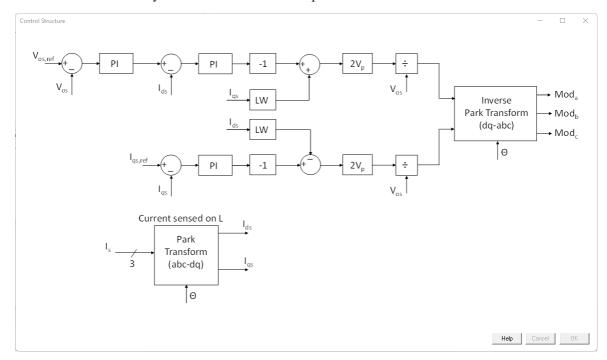

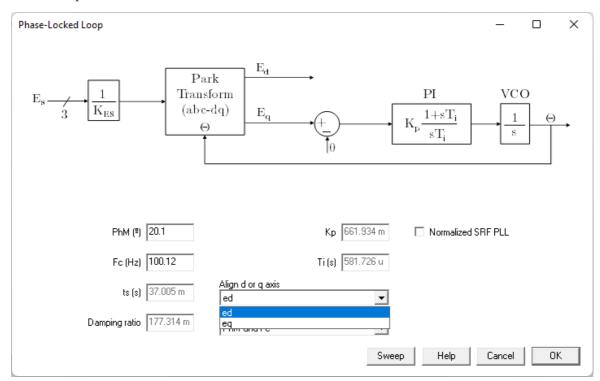

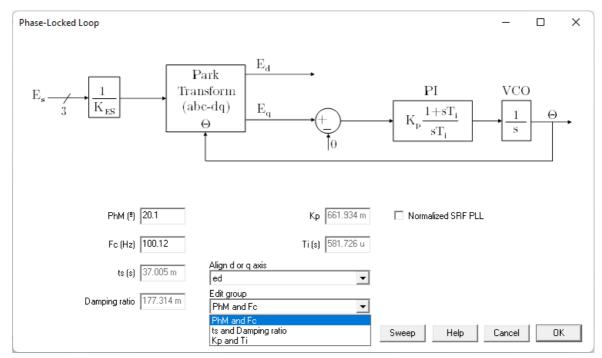

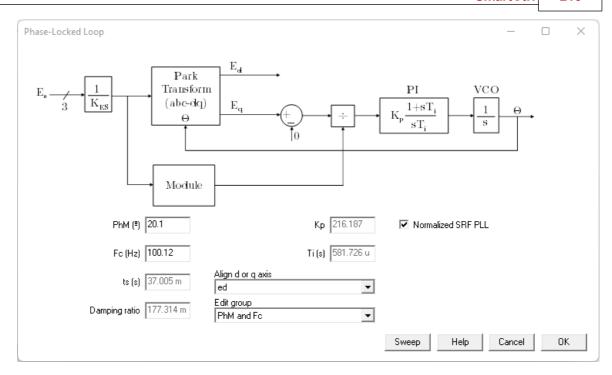

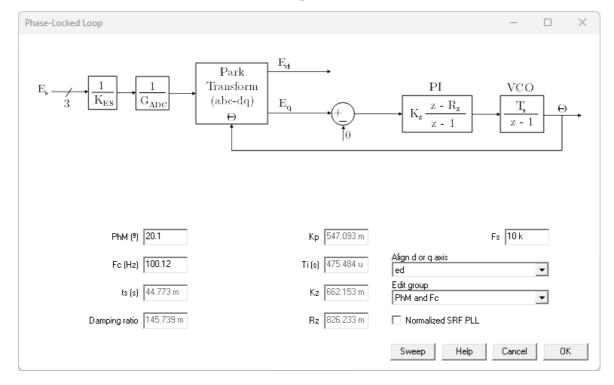

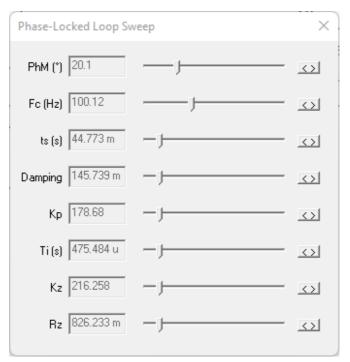

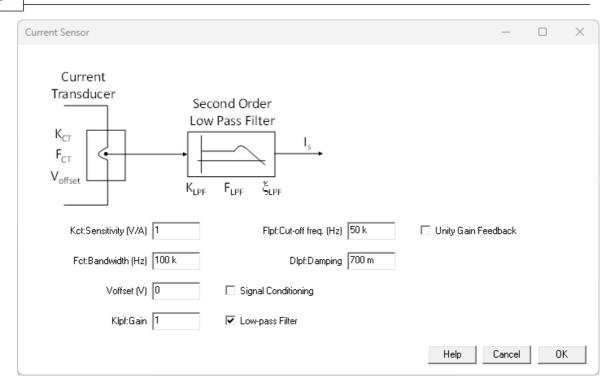

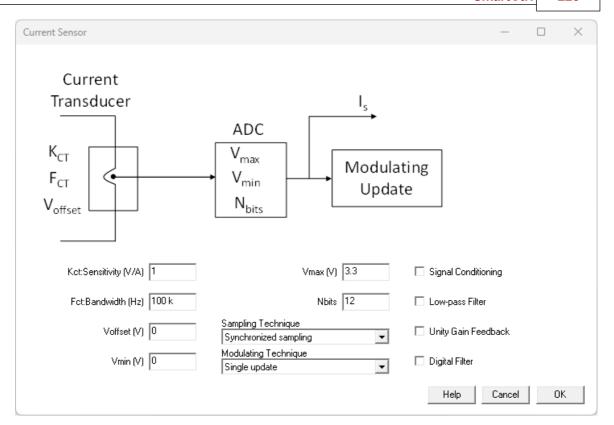

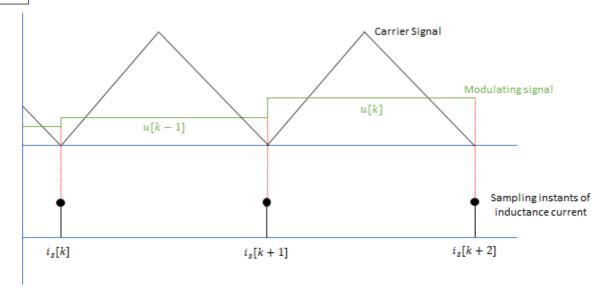

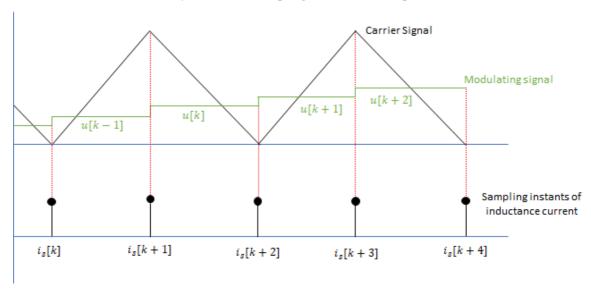

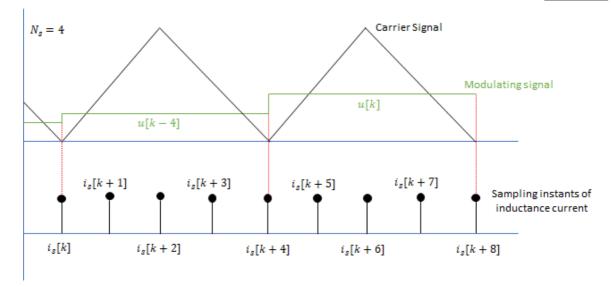

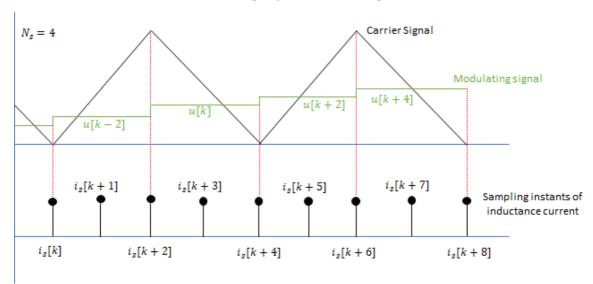

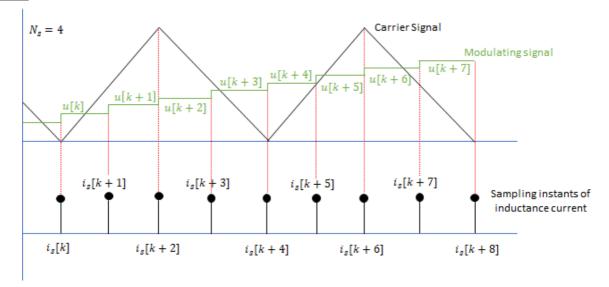

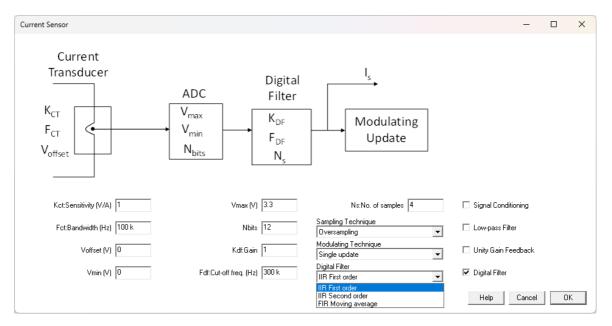

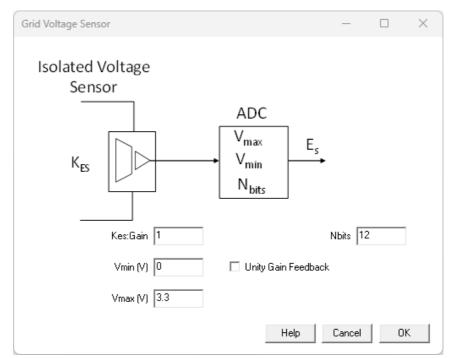

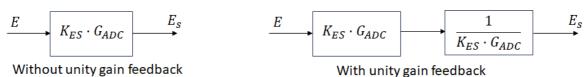

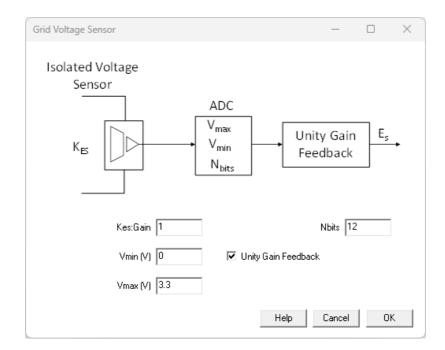

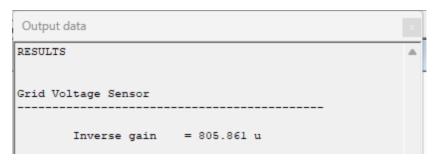

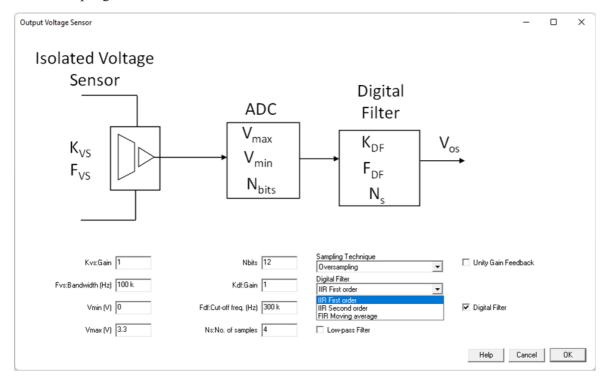

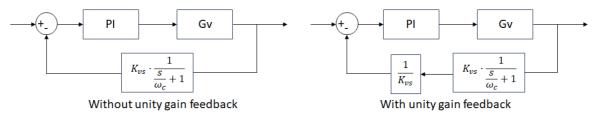

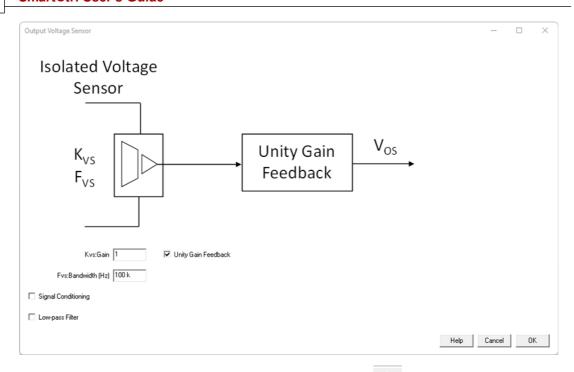

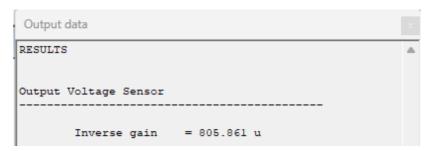

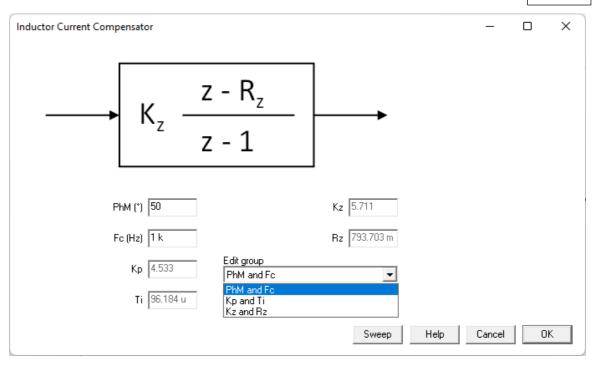

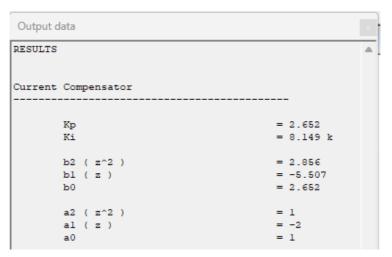

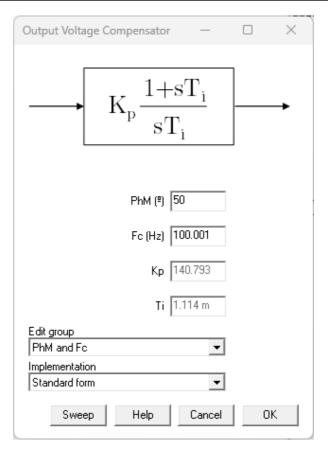

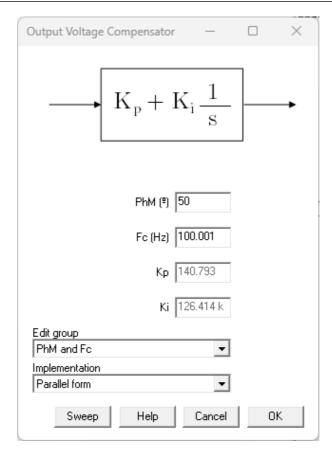

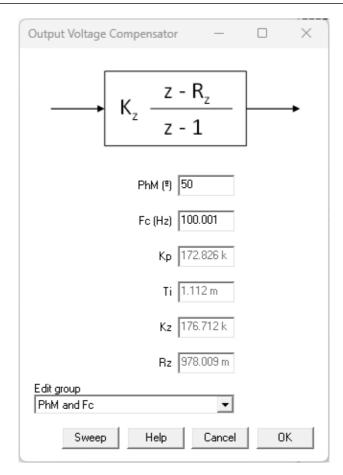

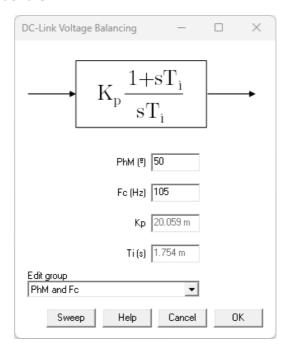

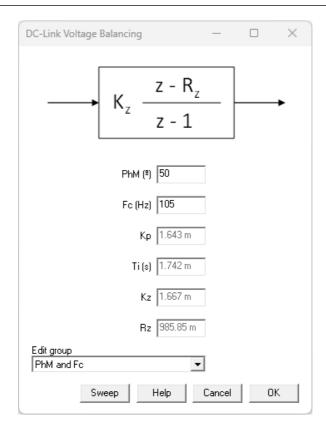

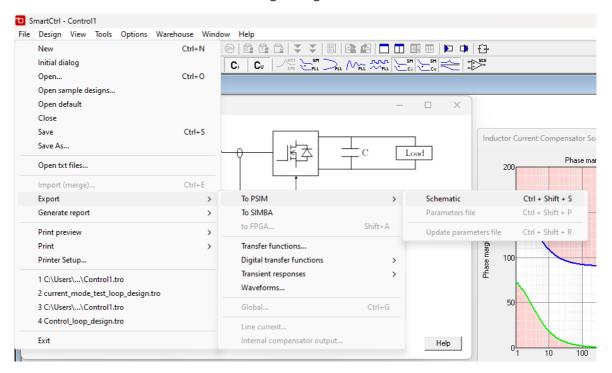

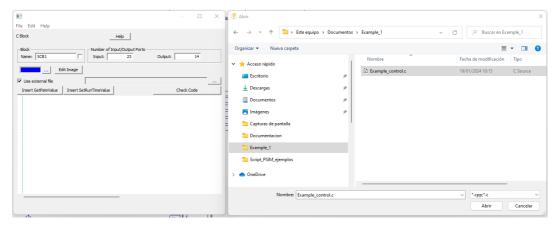

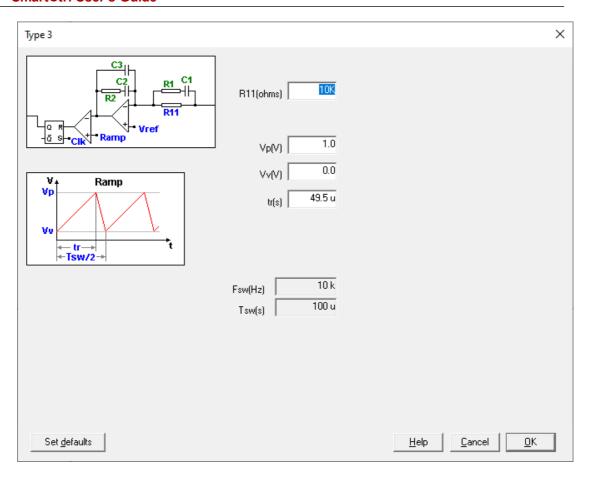

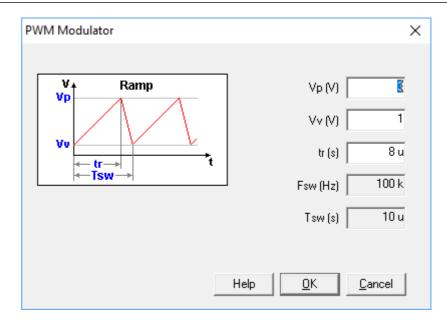

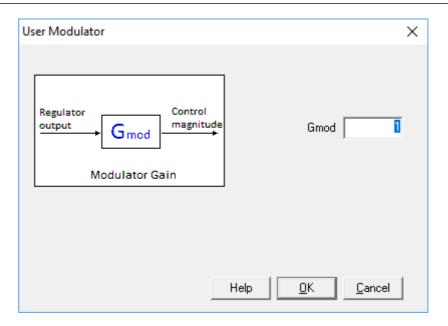

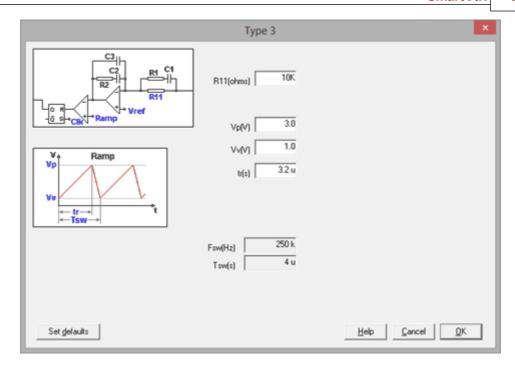

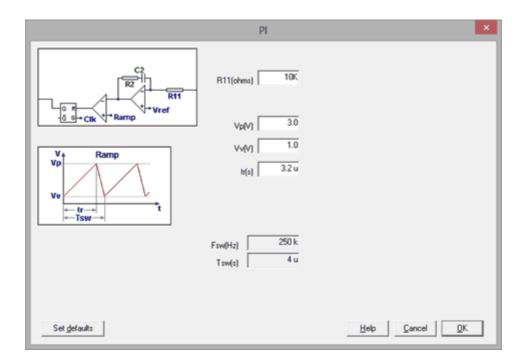

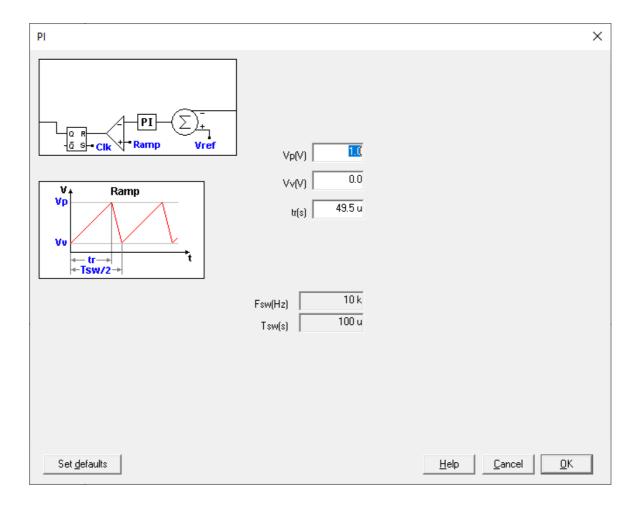

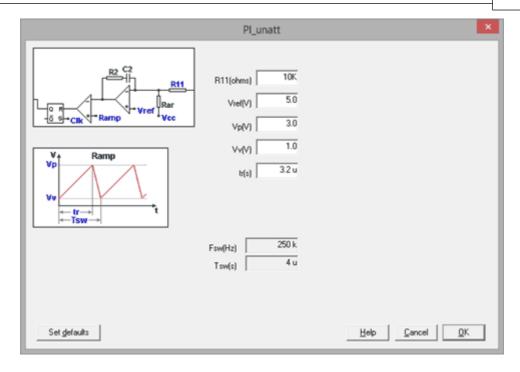

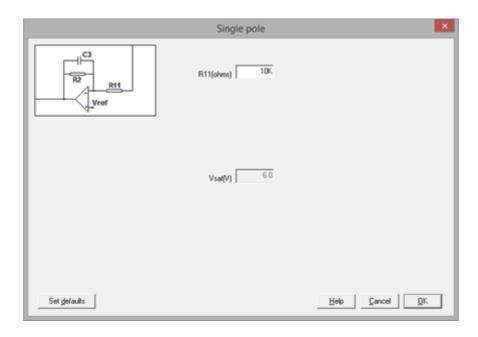

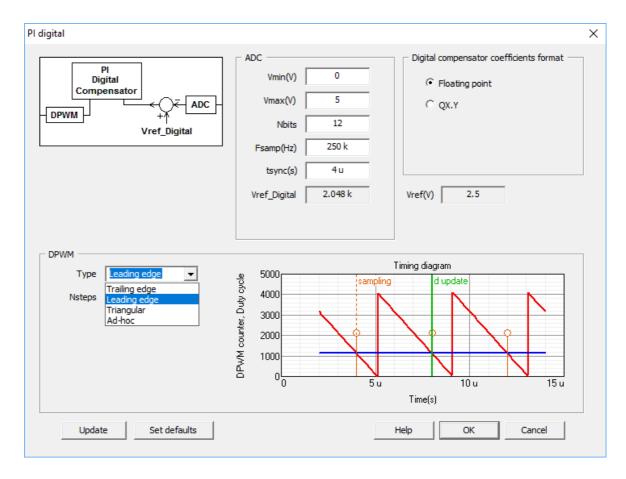

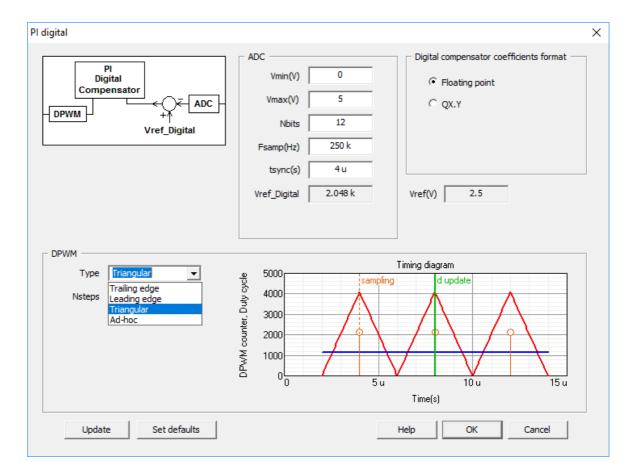

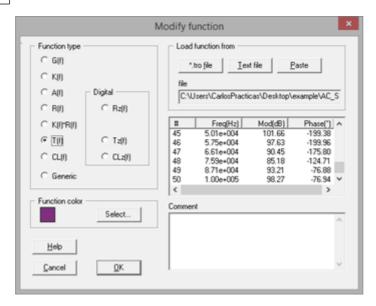

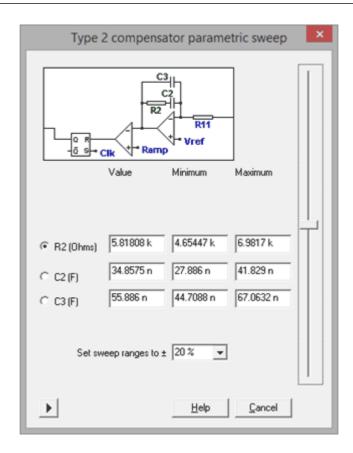

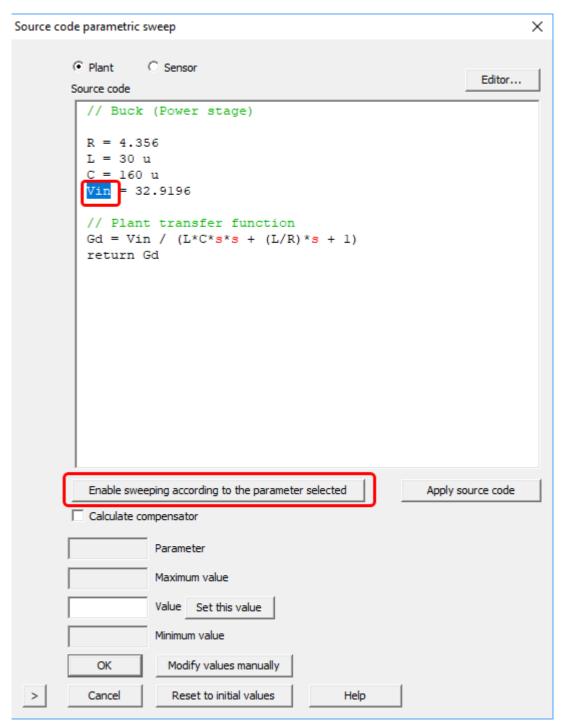

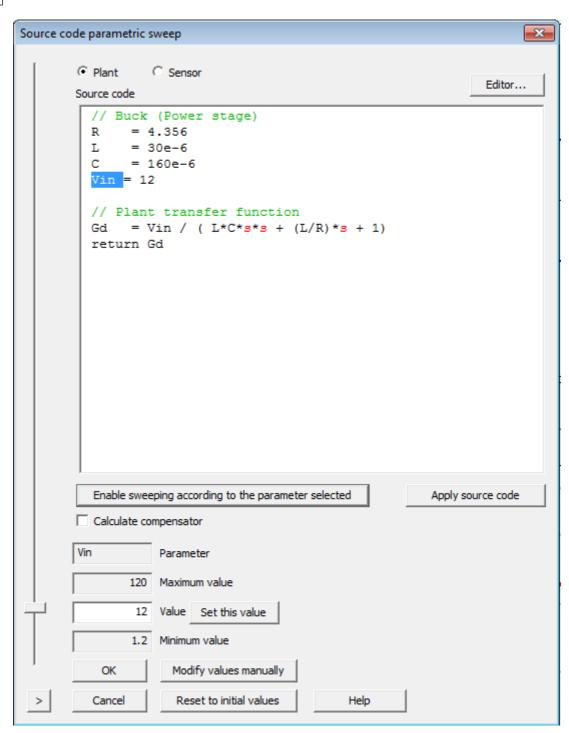

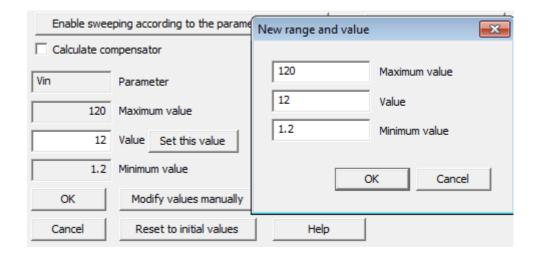

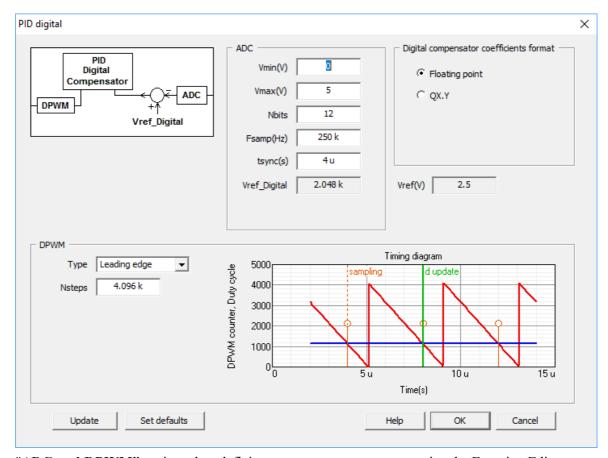

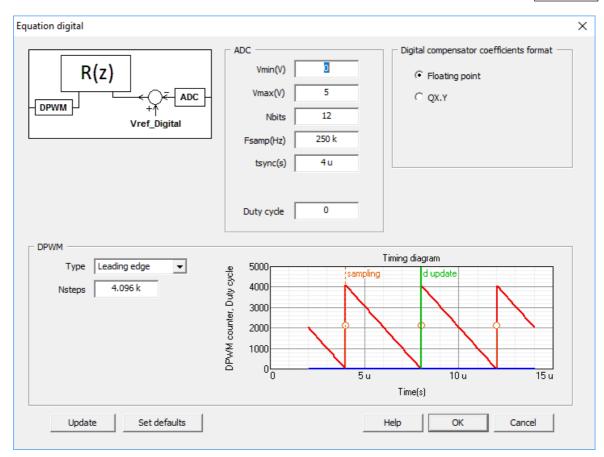

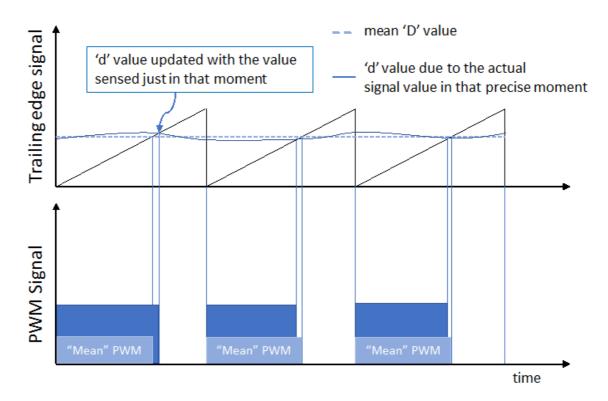

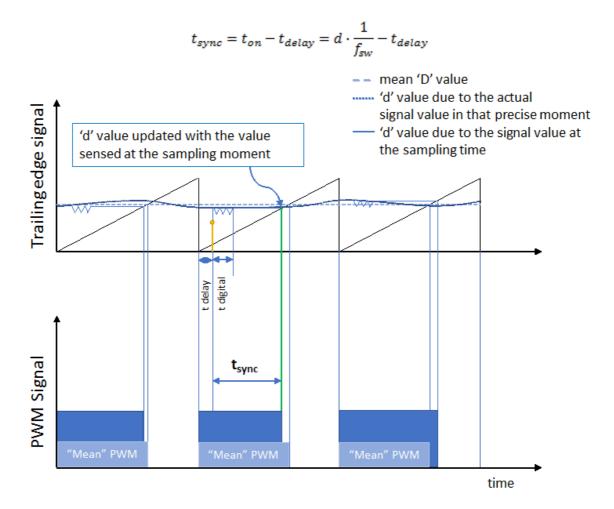

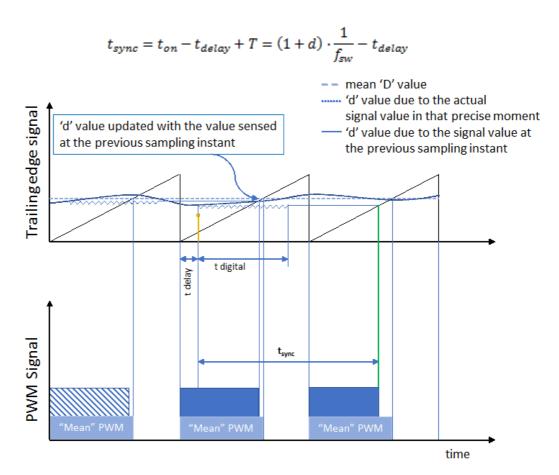

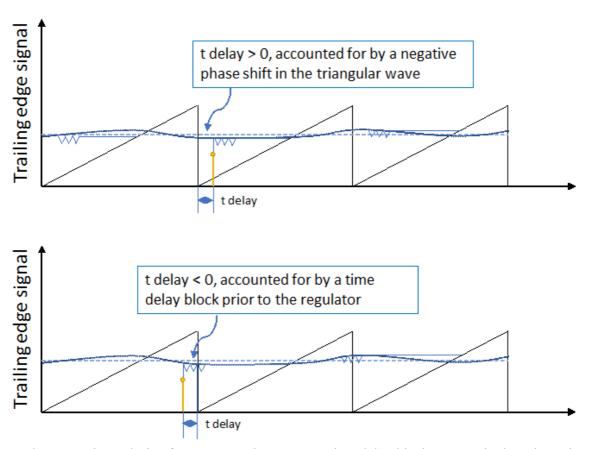

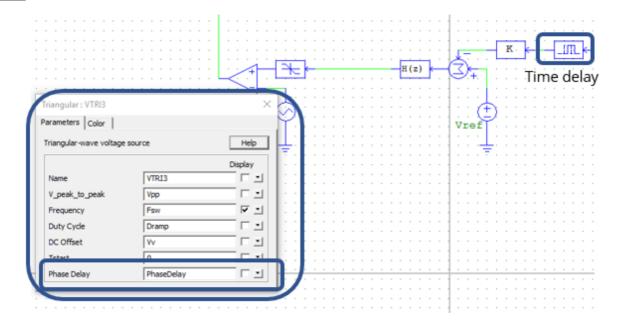

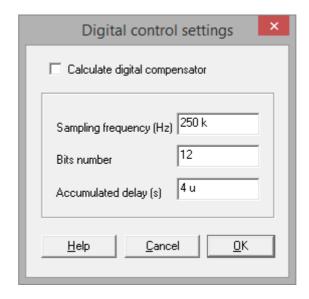

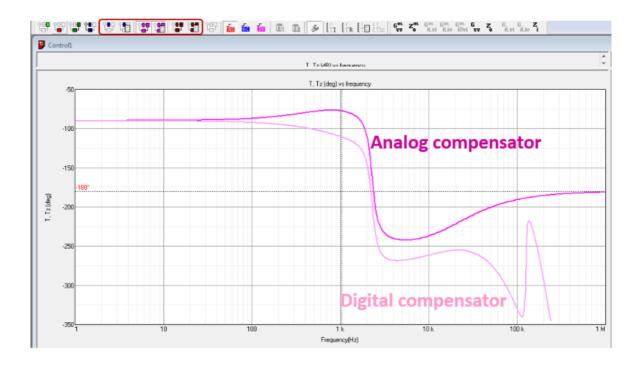

When the s-domain model is intended for Voltage Mode Control (VMC), then the output voltage and the switching frequency must be specified. As highlighted in the next picture: